程式碼下載

電容式感測 Pmod 控制器(頂層檔案):pmod_cdc_ad7156.vhd (15.6 KB)

I2C 主控(也必須包含在專案中):i2c_master.vhd (14.1 KB)

特點

- Digilent Pmod CDC1(適用於 ADI 的 AD7156 電容數位轉換器的 Pmod)精簡介面的 VHDL 原始碼

- 透過平行介面持續輸出每個通道的最新電容數據

- 處理 I2C 通訊以及從電容轉換器 Pmod 檢索所有數據

- 提供 AD7156 電容轉換器的選用使用者自訂配置

- 可設定的系統時脈頻率

介紹

本文詳細介紹了一個 VHDL 組件,用於處理與 Digilent 電容式感測 AD7156 Pmod 的接口,如圖 1 所示。圖 2 展示了此電容式感測 Pmod 控制器整合到系統中的典型範例。如圖所示,此電容式感測 Pmod 控制器連接到 Pmod 連接埠並執行傳輸以配置電容轉換器並收集資料。資料會持續更新並顯示在簡單的平行介面上,這些介面可以連接到使用者邏輯或 FPGA 的輸出連接埠。

圖 1. Digilent 電容式感測 AD7156 Pmod

圖 2. 範例實現

背景

ADI AD7156 是一款雙通道電容數位轉換器(CDC),具有固定閾值模式和自適應環境補償模式。

工作原理

電容式感測 Pmod 控制器主要由狀態機和 I2C 主控組件組成。

狀態機

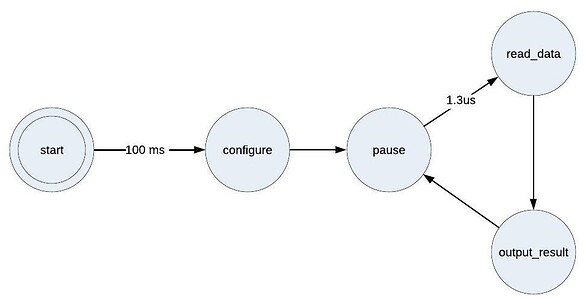

此設計使用圖 3 所示的狀態機來實現其操作。啟動後,組件立即進入 start 狀態。它會在此狀態保持 100ms,以確保 Pmod 有足夠的時間完成上電。然後,它會進入configure 狀態,根據使用者可變更的值配置電容轉換器的模式、閾值、靈敏度等。pause 狀態會根據 AD7156 規格書的要求,在 I2C 傳輸之間插入 1.3us 的「匯流排空閒時間」。在接下來的 read_data 狀態中,它會從 Pmod 的電容轉換器收集最新的電容資料。最後,它會在 output_result 狀態中輸出所有資料。然後,它會在 pause 、read_data 和 output_result 狀態之間不斷循環,以保持電容資料的定期更新。雖然圖中沒有顯示,但任何時候重置組件都會使其回到 start 狀態。

I2C 主控

在 configure 和 read_data 狀態下,狀態機控制 I2C 主控元件與 Pmod 上的電容轉換器通訊。 I2C 主控的文件可在此處取得。

配置電容式感測 Pmod 控制器

電容式感測 Pmod 控制器的配置是透過設定實體中的通用參數來實現的。

系統時脈頻率

通用參數 sys_clk_freq 必須設定為電容式感測 Pmod 控制器在其 clk 連接埠上提供的系統時脈頻率。

AD7156 配置

電容式感測 Pmod 控制器具有七個通用參數,分別對應 AD7156 中的七個暫存器,如表 1 所示。指派給這些通用參數的值在配置狀態下寫入暫存器。程式碼中的預設值與出廠預設暫存器值相同。AD7156 規格書 AD7156.pdf (527.3 KB) 描述了每個暫存器位,因此使用者可以根據需要配置轉換器。

表 1. 用於設定的 AD7156 暫存器對應通用參數

連接埠描述

表 2 描述了電容式感測 Pmod 控制器的連接埠。

表 2. 連接埠描述

連接

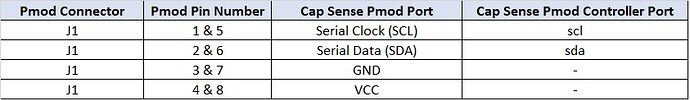

此 Pmod 有一個 8 針連接器。表 3 提供了此連接器的引腳排列。電容式感測 Pmod 控制器的連接埠需要指派給連接到此連接器的 FPGA 引腳,具體如下表所示。J1 連接器的兩排在 Pmod 板上連接在一起,因此只需將一側連接到 FPGA。

表 3. 電容式感測 Pmod 引腳排列及與電容式感測 Pmod 控制器的連接

重置

reset_n 輸入連接埠必須為邏輯高電平,電容式感測 Pmod 控制器組件才能運作。此連接埠上的邏輯低電平會非同步重置元件。重置期間,元件會中止目前與 Pmod 的傳輸,並清除 cdc_ch1_data、cdc_ch2_data、cdc_ch1_avg 和 cdc_ch2_avg 資料輸出以及 i2c_ack_err 輸出。重置解除後,電容式感測 Pmod 控制器將重新啟動工作。它會重新配置電容轉換器,並恢復電容資料的採集和輸出。

結論

這款電容式感測 AD7156 Pmod 控制器是一款可編程式邏輯元件,可與 Digilent 的 Pmod CDC1(電容式感測 AD7156 Pmod)介接。它負責處理與該 Pmod 的所有通訊,以配置 Pmod 的電容轉換器,並在平行輸出上提供持續更新的電容資料流。

更多資訊

AD7156.pdf (527.3 KB)