程式碼下載

spi_to_i2c_bridge.vhd (8.6 KB)

spi_slave.vhd (8.1 KB)

spi_to_i2c.vhd (7.0 KB)

i2c_master.vhd (12.9 KB)

特點

- SPI 轉 I2C 橋接器的 VHDL 原始碼

- 使用者可定義系統時脈

- 使用者可定義 SPI 模式

- 使用者可定義 I2C 串列時脈頻率

- 用於寫入和/或讀取 8-bit I2C 從裝置暫存器

- 將任何 I2C 從設備確認錯誤通知 SPI 主設備

- 符合 NXP UM10204 I2C 總線規格(單主設備匯流排)

- 使用 7-bit I2C 從裝置尋址

- 相容 I2C 從裝置的時脈延展

- 不建議用於多主設備 I2C 匯流排(無仲裁或同步)

介紹

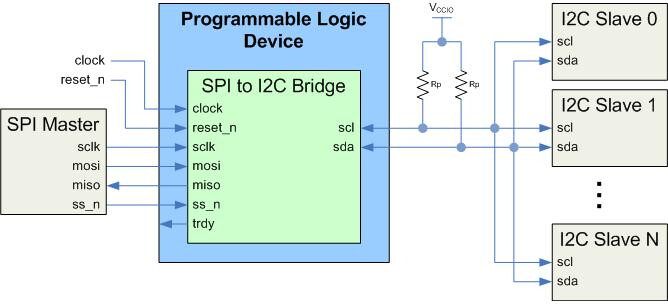

本文詳細介紹了用於單一主 I2C 匯流排的 SPI 轉 I2C 橋接組件,該組件採用 VHDL 語言編寫,適用於 CPLD 和 FPGA。此橋接組件旨在使 SPI 主設備能夠寫入和/或讀取 8-bit I2C 從暫存器。它使用 Quartus II 11.1 版本設計。資源需求取決於具體實現。圖 1 展示了整合到系統中的 SPI 轉 I2C 橋接組件的典型範例。

圖 1. SPI 轉 I2C 橋接實作範例

背景

SPI 和 I2C 都是常用的序列通訊協定。

SPI

SPI 通訊方案是一種全雙工數據連結,使用四線。主機透過將從機選擇( Slave Select ,SS)線拉低來啟動交易。由主機驅動的串列時脈(SCLK)線提供同步時脈來源。主機透過主機輸出、從機輸入(MOSI)線發送數據,並透過主機輸入、從機輸出(MISO)線接收數據。

主機可以透過多種技術與多個從機通訊。在最常見的配置中,每個從機都有獨立的 SS 線,但與其他從機共享 SCLK、MISO 和 MOSI 線。當 SS 線未拉低時,每個從機都會忽略共用線。

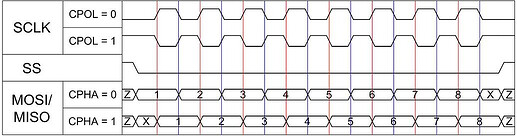

SPI 有四種工作模式,基於兩個參數:時脈極性(CPOL)和時脈相位(CPHA)。主機和從機必須使用相同的模式才能清楚地通訊。如果 CPOL 為 0,則 SCLK 通常為低,第一個時脈邊緣為上升邊緣。如果 CPOL 為 1,則 SCLK 通常為高,第一個時脈邊緣為下降邊緣。CPHA 定義資料對齊方式。如果 CPHA 為 0,則第一個資料位元在 SS 下降邊緣寫入,並在第一個 SCLK 邊緣讀取。如果 CPHA 為 1,則資料在第一個 SCLK 邊緣寫入,並在第二個 SCLK 邊緣讀取。圖 2 中的時序圖描述了四種 SPI 模式。

圖 2. SPI 時序圖

I2C

I2C 總線是由 Philips(現為 NXP)發明並指定的雙線半雙工資料鏈路。I2C 總線的兩條線,SDA 和 SCL,是雙向的,並且是開汲極的,由電阻上拉。 SCL 是串列時脈線,SDA 是串列資料線。總線上的設備將一條線拉至地以發送邏輯 0,將另一條線(保持浮起)釋放以發送邏輯 1。

更多信息,請參閱下方「附加資訊」部分中附帶的 I2C 規範。該規範詳細解釋了協議、電氣規格、上拉電阻的大小等。

工作原理

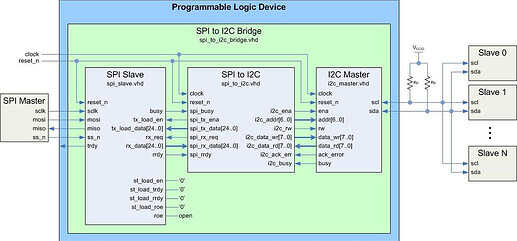

SPI 轉 I2C 橋接器的原始碼由以下四個 VHDL 檔案組成:

- spi_to_i2c_bridge.vhd

- spi_slave.vhd

- spi_to_i2c.vhd

- i2c_master.vhd

圖 3 展示了這些文件之間的關係。

圖 3. SPI 轉 I2C 橋接架構

spi_to_i2c_bridge.vhd 檔案是頂層繞接器,用於實例化並將其他三個檔案連接在一起。

spi_slave.vhd 檔案定義了一個 SPI 從設備元件,該元件可直接與外部 SPI 主設備介面。此 SPI 從設備組件(v1.2)的詳細文件可在此處取得。

同樣,i2c_master.vhd 定義了一個 I2C 主設備組件,該組件可直接與 I2C 從設備組件通訊。此 I2C 主設備組件(v2.2)的詳細文件可在此處取得。

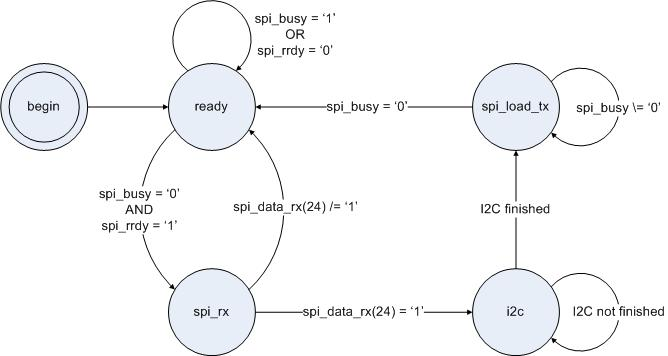

spi_to_i2c.vhd 檔案控制橋接器的操作,並在 SPI 從機和 I2C 主機之間轉換。圖 4 中的狀態圖描述了其操作。橋接器處於就緒狀態,監控 SPI 從機的忙碌訊號及其接收就緒(rrdy)狀態暫存器。一旦 SPI 從機接收到來自 SPI 主機的新資料傳輸,rrdy 連接埠就會置位。忙線訊號指示 SPI 從機何時可用。一旦滿足這兩個條件,橋接器就會向從機請求新的 SPI 資料並進入 spi_rx 狀態。然後,新的 SPI 資料會被閂鎖。如果資料包含執行 I2C 交易的命令(位元 25 為「1」),則橋接器進入 i2c 狀態。如果指令未要求 I2C 傳輸(位元 25 為「0」),則橋接器會傳回就緒狀態。進入 i2c 狀態後,橋接器邏輯將使用 I2C 主機元件透過 I2C 匯流排執行交易。此傳輸需要多個時脈週期。其持續時間取決於 I2C 序列匯流排速度、系統時脈以及從機是否進行時脈延長。完成後,橋接器進入 spi_load_tx 狀態。它會等待 SPI 從機空閒,然後將 I2C 傳輸的結果寫入從機的傳送暫存器,並傳回就緒狀態。當橋接器將傳送暫存器載入到傳送暫存器時,SPI 從機的傳送就緒(trdy)狀態暫存器將置位,表示 I2C 結果現在可供 SPI 主機檢索,並且橋接器已準備好進行下一個交易。 SPI 主機可以透過使用 trdy 連接埠的引腳中斷或透過 SPI 匯流排本身輪詢 SPI 從機的狀態暫存器來接收 trdy 訊號。

圖 4. SPI 轉 I2C 狀態機

為簡單起見,狀態圖中未顯示重置功能。如果 reset_n 連接埠在任何時候被拉低,橋接器將重新初始化,狀態機將返回就緒狀態。

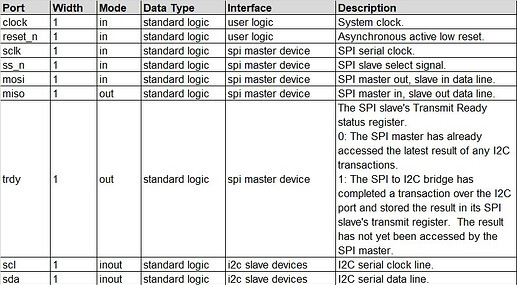

連接埠描述

表 1 描述了 SPI 轉 I2C 橋接器的連接埠。

表 1. 連接埠描述

使用者可定義參數

spi_to_i2c_bridge.vhd 檔案是橋接組件的頂層 VHDL 繞接器檔。其 ENTITY 部分定義了四個 GENERIC 參數,構成了組件的使用者可定義部分。

系統時脈

sys_clk_frq 參數必須設定為輸入系統時脈頻率(單位為 Hz)。範例程式碼中的預設設定為 50MHz(元件模擬和測試時的頻率)。

I2C 總線速度

i2c_scl_frq 參數必須設定為 I2C 串列時脈 scl 的所需頻率。範例程式碼中的預設設定為 400kHz,對應於 I2C 規格中的快速模式位元率。

SPI 模式

SPI 介面的工作模式由參數 cpol 和 cpha 定義。 SPI 主設備和 SPI 轉 I2C 橋接器必須工作在同一模式下才能進行通訊。這兩個參數的預設值均為「0」。

執行傳輸

此橋接器實作使 SPI 主裝置能夠寫入和/或讀取 8-bit I2C 從裝置暫存器。橋接器的 SPI 從設備組件與 SPI 主設備之間的每個傳輸都必須包含一個 8-bit 命令,隨後是 25-bit 資料傳輸。因此,要執行傳輸,SPI 主設備需要向從設備發送 33-bit 命令,如表 2 所示。此指令包含 8-bit SPI 從裝置指令、一個 I2C 啟用位元、I2C 從裝置的 7-bit 位址、一個讀/寫位元、一個用於在 I2C 從裝置內部存取的 8-bit 暫存器位址以及用於寫入 I2C 從裝置的 8-bit 資料。該命令以 MSB 優先的方式傳輸。在 8-bit SPI 從設備命令期間,SPI 從設備的 MISO 線保持高阻態,然後在剩餘的 25bits 期間傳回資料。有關完整的時序詳細信息,請參閱此處的 SPI 從設備文件。

表 2. 命令格式

表 2 也列出了執行各種操作所需的命令。SPI 從裝置指令的第一位指定要寫入橋接器 SPI 從裝置中的哪個暫存器。「0」表示 SPI 從裝置的接收暫存器,橋接器在此接收命令並評估要執行的操作。如果 I2C 使能位元為「1」,則橋接器將執行 I2C 傳輸。如果為「0」,橋接器將忽略其餘位,並且在總線上不執行任何操作。此選項允許 SPI 主裝置讀取 I2C 結果或橋接器的狀態暫存器,而無需發出新的 I2C 傳輸。

第二位元指定要傳回 SPI 主裝置的橋接器 SPI 從裝置中的哪個暫存器。「0」表示 SPI 從裝置的傳送暫存器,該暫存器始終保存上一個 I2C 事務的結果。「1」表示 SPI 從裝置的狀態暫存器。 SPI 主機可以讀取狀態暫存器以輪詢 trdy 的值,這是傳回的第一個位元。

最後 24-bit 指定請求的 I2C 傳輸。如果傳輸是讀取,則最後的 8 個數據位元將被忽略。

I2C 傳輸結果

每次 I2C 傳輸結束後,橋接器都會將一個 25bit 結果載入到 SPI 從裝置的傳送暫存器中,SPI 主裝置可從該暫存器中取得該結果,如上所述。表 3 顯示了 I2C 結果的格式。I2C 確認錯誤位元指示交易期間是否發生了任何 I2C 從裝置確認錯誤。(「1」表示至少發生了一個錯誤,「0」表示沒有錯誤。)如果發生確認錯誤,橋接器不會重試傳輸,因此如果 SPI 主設備希望重試通訊,則必須重新發出命令。7-bit I2C 從裝置位址、讀/寫位元和 8-bit I2C 從裝置暫存器指示發送了什麼命令。如果命令是讀取命令,則 8-bit 資料位元會傳回讀取的資料;如果命令是寫入命令,則傳回寫入的資料。

![]()

表 3. I2C 結果格式

時脈伸展

I2C 規格第 3.1.9 節定義了一個選用功能,即從裝置可以將 scl 保持為低電平,從而暫停傳輸。某些從設備設計為在繼續操作之前需要更多時間儲存接收到的資料時執行此操作。此 I2C 主設備組件與此功能的從設備相容。它無需控制 I2C 主設備的使用者進行任何操作。

重置

reset_n 輸入連接埠必須為邏輯高電平,SPI 轉 I2C 橋接組件才能運作。此連接埠上的邏輯低電平會非同步重置元件。在重置期間,miso、scl 和 sda 連接埠將呈現高阻態,trdy 暫存器將被清除。

結論

此 SPI 轉 I2C 橋接器是一款可編程邏輯元件,可讓 SPI 主裝置寫入和/或讀取 8-bit I2C 從屬暫存器。它提供使用者可定義的 SPI 模式、I2C 匯流排頻率和系統時脈頻率。它遵循 NXP I2C 單主匯流排規範,並包含可選的時脈延長功能。

附加資訊

UM10204, I2C-bus specification and user manual, NXP Semiconductors N.V. (1.3 MB)