Serielle Peripherie-Schnittstelle (SPI) Master (VHDL) – Logik - eewiki (digikey.com)

Erstellt von Scott Larson, zuletzt geändert am 06. Februar 2021

Code Download - herunterladen

Eigenschaften / Merkmale

Einführung

Hintergrund

Port-Beschreibungen

Taktung

Polarität und Phase

Transaktionen

Kontinuierlicher Modus

Zurücksetzen

Fazit

Verwandte Themen

Kontakt

Code-Download

Version 1.1: spi_master.vhd

ModelSim-Simulationsfehler korrigiert (Signal clk_toggles explizit zurücksetzen)

Version 1.0: spi_master_v1_0.vhd

Erste öffentliche Freigabe

Merkmale

- VHDL-Quellcode einer Serial Peripheral Interface (SPI) Master-Komponente

- Konfigurierbare Anzahl von Slaves

- Konfigurierbare Datenbreite

- Wählbare Polarität und Phase

- Wählbare Geschwindigkeit

- Kontinuierlicher Modus für lange Datenströme

Einführung

Hier wird ein SPI-Master-Baustein für den Einsatz in CPLDs und FPGAs beschrieben, der in VHDL geschrieben wurde. Der Baustein wurde mit Quartus II, Version 9.0, entwickelt. Der Ressourcenbedarf ist abhängig von der Implementierung (d.h. von der gewünschten Anzahl der Slaves und der Datenbreite). Abbildung 1 zeigt ein typisches Beispiel für die Integration des SPI-Masters in ein System.

Abbildung 1. Beispielanwendung

Hintergrund

Ein SPI-Kommunikationsschema ist eine Vollduplex-Datenverbindung, die vier Drähte verwendet. Der Master initiiert die Transaktion, indem er die Slave Select (SS)-Leitung auf low zieht. Eine serielle Taktleitung (SCLK), die vom Master getrieben wird, liefert eine synchrone Taktquelle. Der Master sendet Daten über die Leitung Master Out, Slave In (MOSI) und empfängt Daten über die Leitung Master In, Slave Out (MISO).

Ein Master kann mit mehreren Slaves über eine Vielzahl von Techniken kommunizieren. In der gängigsten Konfiguration hat jeder Slave eine unabhängige SS-Leitung, teilt sich aber die SCLK-, MISO- und MOSI-Leitungen mit den anderen Slaves. Jeder Slave ignoriert die gemeinsam genutzten Leitungen, wenn seine SS-Leitung nicht auf low gezogen ist. Diese Topologie ist in Abbildung 1 oben dargestellt.

SPI hat vier Betriebsmodi, die auf zwei Parametern basieren: Taktpolarität (CPOL) und Taktphase (CPHA). Master und Slave müssen denselben Modus verwenden, um artikulativ zu kommunizieren. Wenn CPOL Null ist, dann ist SCLK normalerweise niedrig und die erste Taktflanke ist eine steigende Flanke. Wenn CPOL eins ist, ist SCLK normalerweise high, und die erste Taktflanke ist eine fallende Flanke. CPHA definiert die Datenausrichtung. Wenn CPHA gleich Null ist, wird das erste Datenbit mit der fallenden Flanke von SS geschrieben und mit der ersten SCLK-Flanke gelesen. Wenn CPHA eins ist, werden die Daten bei der ersten SCLK-Flanke geschrieben und bei der zweiten SCLK-Flanke gelesen. Das Timing-Diagramm in Abbildung 2 stellt die vier SPI-Modi dar.

Abbildung 2. SPI-Timing-Diagramm

Port-Beschreibungen

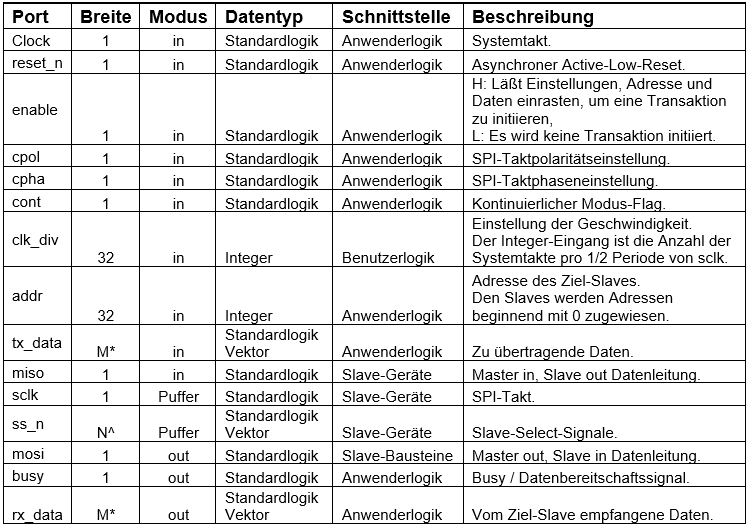

Tabelle 1 beschreibt die Ports des SPI-Masters. Die Anzahl der Slaves wird in der ENTITY durch den GENERIC-Parameter slaves und die Sende- und Empfangsdatenbusbreite durch den GENERIC-Parameter d_width deklariert.

Tabelle 1. Port-Beschreibungen

Hinweise

- M ist die angegebene Datenbreite, eingestellt durch die Generik d_width

^ N ist die angegebene Anzahl der Slaves, eingestellt durch die Slaves-Generik

Taktung

Die Eingänge clock und clk_div definieren die Frequenz von SCLK (d.h. die SPI-Datenrate). clock ist der Systemtakt, der für den Betrieb der synchronen Logik innerhalb des Bausteins verwendet wird. Mit dem Integer-Eingang clk_div kann der Anwender die relative Geschwindigkeit einstellen, mit der die aktuelle Transaktion erfolgt. clk_div ist die Anzahl der Taktperioden zwischen den SCLK-Übergängen, wie in Gleichung 1 beschrieben.

(1)

Wenn der Anschluss clk_div auf 1 gesetzt ist, beträgt die SCLK-Frequenz die Hälfte der Taktfrequenz und ist auf die maximal erreichbare Datenrate eingestellt. Der Enable-Pin latcht den Wert von clk_div in den Baustein, um jede Transaktion zu beginnen, sodaß es möglich ist, die Datenrate für einzelne Slaves anzupassen.

Das Setzen des Ports clk_div auf einen konstanten Wert legt die Datenrate dauerhaft fest. Wird clk_div auf 0 gesetzt, nimmt der Baustein den Wert 1 an. Das Binden des Ports clk_div auf low konfiguriert den Baustein daher so, daß er immer mit maximaler Geschwindigkeit arbeitet.

Polarität und Phase

Der Enable-Pin verriegelt zu Beginn jeder Transaktion die logischen Standardwerte von cpol und cpha. Dies ermöglicht die Kommunikation mit einzelnen Slaves in unabhängigen SPI-Modi. Wenn alle Slaves den gleichen Modus benötigen, können cpol und cpha einfach auf die entsprechenden Logikpegel gebunden werden.

Transaktionen

Ein niedriger Logikpegel am Busy-Ausgang zeigt an, daß der Baustein bereit ist, einen Befehl zu akzeptieren. Der Baustein speichert die Einstellungen, die Adresse und die Daten für eine Transaktion bei der ersten steigenden Flanke des Taktes, bei der der Freigabeeingang aktiviert wird. Mit der folgenden Taktflanke setzt der Baustein das Busy-Signal und beginnt mit der Durchführung der Transaktion. Nach Abschluß der Transaktion gibt der Baustein die empfangenen Daten auf dem Port rx_data aus. Diese Daten verbleiben auf dem Port, bis der Baustein neue Daten von einer nachfolgenden Transaktion empfängt. Die Komponente setzt busy auf low, um den Anwender zu informieren, wenn die Daten verfügbar sind, und die Komponente ist sofort bereit für einen weiteren Befehl.

Abbildung 3 zeigt das Timing-Diagramm für eine typische Transaktion. Dieser SPI-Master ist mit vier Slaves und einer Datenbreite von vier Bit instanziiert. Er sendet die Daten “1001” an den Slave 2, der im SPI-Modus 3 (CPOL = 1, CPHA = 1) arbeitet. Der Master empfängt die Daten “1010”.

Abbildung 3. Typisches Transaktions-Timing-Diagramm

Kontinuierlicher Modus

Während des letzten Empfangsbits liest der SPI-Master das Cont-Flag. Wenn es low ist, schließt der Baustein die Kommunikation wie oben beschrieben ab. Wenn es high ist, speichert der Baustein die Daten auf dem tx_data-Port und setzt die Übertragung mit den neuen Daten nahtlos fort, sobald die aktuellen Daten aufgebraucht sind. Wenn das letzte Bit der aktuellen Daten zu Ende ist (d.h. wenn das erste Bit der neuen Daten auf dem mosi-Port erscheint), gibt der Baustein den ersten Block der Empfangsdaten auf dem rx_data-Port aus und läßt das Busy-Signal für einen Taktzyklus erlöschen, um anzuzeigen, daß diese Empfangsdaten verfügbar sind. Die Empfangsdaten verbleiben am rx_data-Port, bis die neue Datenkommunikation abgeschlossen ist und der Baustein den nachfolgenden Empfangsdatenblock ausgibt.

In Abbildung 4 ist das Timing-Diagramm für eine Transaktion im Continuous Mode dargestellt. Dieser SPI-Master wird mit vier Slaves und einer Datenbreite von zwei Bit instanziiert. Nachdem der Baustein die ersten Daten “10” gelatcht hat, bleibt der cont-Port auf High und der tx_data-Port präsentiert die neuen Daten “01”. Nachdem der Baustein die neuen Daten gelatcht hat, setzt er den Busy-Port auf Low, was signalisiert, daß der Cont- und der tx_data-Port gelöscht werden können und daß die ersten Empfangsdaten “01” am rx_data-Port anliegen. Wenn die Transaktion abgeschlossen ist, wird das Busy-Signal wieder deassert und die neuen rx_data “10” sind verfügbar.

Abbildung 4. Transaktions-Zeitdiagramm mit Continuous Mode

Der Continuous Mode kann sehr lange Datenströme abwickeln, da er permanent implementiert ist. Das Binden des cont-Ports auf low deaktiviert den kontinuierlichen Modus.

Reset

Der reset_n-Eingangsport muß ein logisches High haben, damit die SPI-Master-Komponente funktioniert. Ein Low-Signal an diesem Port setzt den Baustein asynchron zurück. Während des Resets hält der Baustein den Busy-Port und alle ss_n-Ausgänge auf high. Der mosi-Ausgang nimmt einen hochohmigen Zustand an und der rx_data-Ausgangsport wird gelöscht. Nach dem Reset wird der Busy-Port mit dem nächsten Takt deassert und zeigt damit die Kommunikationsbereitschaft des SPI-Masters an.

Fazit

Dieser SPI-Master ist ein flexibler programmierbarer Logikbaustein, der die Kommunikation mit einer Vielzahl von Slaves über eine einzige parallele Schnittstelle ermöglicht. Er ermöglicht die Kommunikation mit einer benutzerdefinierten Anzahl von Slaves, die unabhängige SPI-Modi, Datenbreiten und serielle Taktgeschwindigkeiten erfordern können.

Verwandte Themen

Serial Peripheral Interface (SPI) Slave (VHDL)

SPI 3-Wire Master (VHDL)

SPI to I²C Bridge (VHDL)

Accelerometer ADXL345 Pmod Controller (VHDL) – Dieses Design verwendet die auf dieser Seite beschriebene SPI Master Komponente, um mit einem Analog Devices ADXL345BCCZ-RL Accelerometer zu kommunizieren. Es demonstriert auch die Verwendung der Continuous-Mode-Funktion dieses SPI-Masters.

Accelerometer ADXL362 Pmod Controller (VHDL) – Dieses Design verwendet die auf dieser Seite beschriebene SPI-Master-Komponente zur Kommunikation mit einem ADXL362BCCZ-R2 Accelerometer von Analog Devices. Es demonstriert auch die Verwendung der Continuous-Mode-Funktion dieses SPI-Masters.

Ambient Light Sensor Pmod Controller (VHDL) – Dieses Design verwendet die auf dieser Seite beschriebene SPI-Master-Komponente zur Kommunikation mit einem ADC.

ADC AD7476A Pmod Controller (VHDL) – Dieses Design verwendet eine Version dieses SPI-Master-Bausteins, die so modifiziert wurde, daß sie eine zweite MISO-Datenleitung enthält. Mit 2 Dateneingangsleitungen kommuniziert das Design mit (empfängt Daten von) 2 separaten ADCs gleichzeitig.

DAC AD5628 Pmod Controller (VHDL) – Dieses Design verwendet den obigen SPI Master, um mit einem Analog Devices AD5628ARUZ-2 12-Bit Digital-Analog-Wandler zu kommunizieren. Es konfiguriert den Wandler und sendet Befehle, Adressen und Daten zur Steuerung der 8 Kanäle des Wandlers.

DAC DAC121S101 Pmod Controller (VHDL) – Dieses Design verwendet eine Version dieser SPI-Master-Komponente, die so modifiziert wurde, daß sie eine zweite MOSI-Datenleitung enthält. Mit den 2 Datenausgangsleitungen sendet das Design identische Daten gleichzeitig an 2 separate DACs.

Thermocouple Pmod Controller (VHDL) – Dieses Design verwendet den oben genannten SPI-Master, um Informationen von einem Maxim MAX31855SASA+T Thermoelement-Digital-Wandler abzurufen.

Kontakt

Kommentare, Feedback und Fragen können direkt an eewiki@digikey.com gesendet werden.