程式碼下載

7 段顯示器驅動程式(頂層檔案):

版本 1.1:seven_segments.vhd (5.0 KB)

新增了用於配置 7 段顯示器極性的通用參數

版本 1.0:seven_segments_v1_0.vhd (4.4 KB)

首次公開發布

二進位到 BCD 轉換器(必須包含在專案中):binary_to_bcd.vhd (5.8 KB)

二進位到 BCD 數位轉換器(必須包含在專案中):binary_to_bcd_digit.vhd (3.2 KB)

BCD 到 7 段顯示器對應(必須包含在專案中):bcd_to_7seg_display.vhd (2.0 KB)

特點

- 7 段顯示器驅動程式的 VHDL 原始碼

- 在 7 段顯示器上顯示多位整數

- 不顯示前導零

- 可配置 7 段顯示器數量

- 可配置顯示的輸入整數值範圍

- 可配置 7 段顯示器極性

介紹

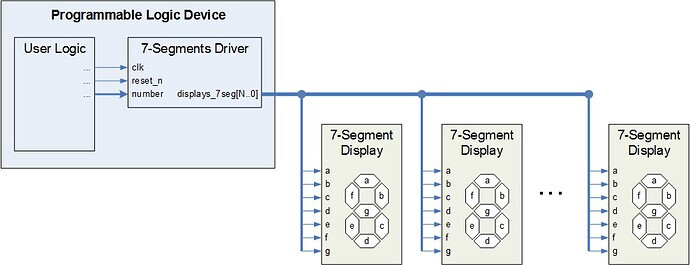

本文詳細介紹了一種用於 CPLD 和 FPGA 的多位 7 段顯示驅動器電路,該電路採用 VHDL 語言編寫。此元件從使用者邏輯讀取一個整數,並將其輸出到所需數量的 7 段顯示器上。對於位數少於顯示寬度的整數,不會顯示前導零。此元件使用 Quartus II 13.1.0 版本設計。資源需求取決於具體實現。圖 1 展示了整合到系統中的 7 段顯示驅動器的典型範例。

圖 1. 範例實現

工作原理

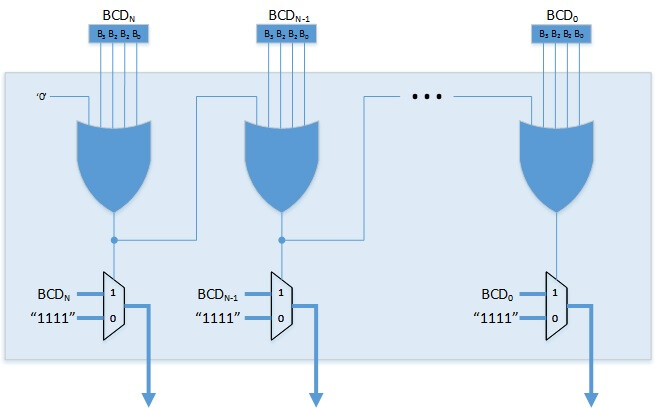

圖 2 展示了此組件在 7 段顯示器上顯示輸入整數的操作。

圖 2. 執行的操作

二進位到 BCD 碼的轉換

此元件使用此處提供的二進位到 BCD 碼轉換器執行二進位到 BCD 碼的轉換。

停用前導零

此元件使用「或」邏輯判斷每個 BCD 位元是否為前導零。結果作為一系列多工器的位址訊號,每個多工器傳遞原始值(非前導零)或將值設為「1111」(如果是前導零)。圖 3 描述了該電路。

圖 3. 移除前導零

此方法有效,因為下一節中所述的 BCD 碼到 7 段碼的對應會在 7 段顯示器接收到非數字 BCD 值(即值大於「1001」)時使其清空。

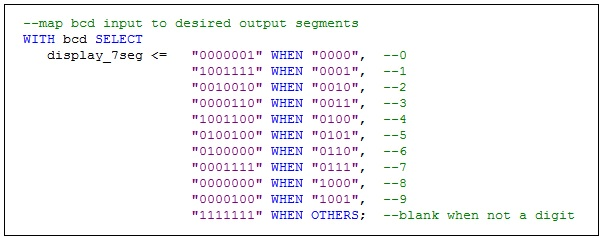

BCD 碼到 7 段碼的對應

bcd_to_7seg_display.vhd 檔案將 BCD 碼對應到 7 段碼輸出,如圖所示。這些輸出採用共陽極 7 段碼顯示配置。seven_segments.vhd 頂層檔案中的多工器選擇將這些值或其反相傳送至輸出埠。ss_polarity 泛型決定了此選擇,具體方法請參閱下文「參數泛型」部分。

參數泛型

元件實體中有三個泛型用於配置元件。

位數

泛型位數設定組件控制的 7 段顯示器的數量。

位元

泛型位元是執行內部二進位到 BCD 碼轉換所必需的。此泛型應設定為以二進位表示輸入整數範圍所需的最大位數。這通常對應於 7 段顯示器上可以顯示的最大位數。表示特定位數所需的最大位數由公式 1 定義。

![]()

答案總是向上捨入(例如,4 位數字需要 3.322*4 = 13.288,向上捨入為 14bit)。

ss_polarity

通用 ss_polarity 設定驅動 7 段顯示器的輸出訊號的極性。如果 7 段顯示器為共陽極(低電平 = 開啟,高電平 = 關閉),則該通用值應設為「0」;如果顯示器為共陰極(高電平 = 開啟,低電平 = 關閉),則該通用值應設為「1」。

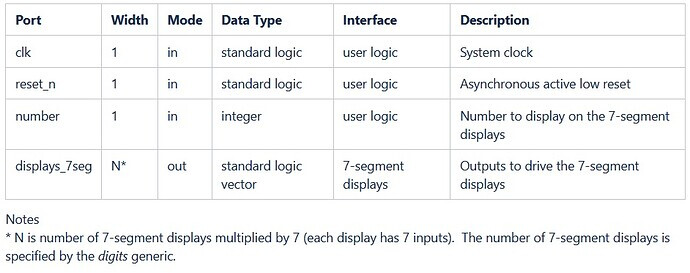

連接埠描述

表 1 描述了 7 段顯示器驅動器的連接埠。

表 1. 連接埠描述

顯示數字

圖 4 展示了一個範例時序圖。在本例中,7 段顯示器的數量配置為 3,如通用數字所示。通用位元設定為 10,因為需要 10 位元來表示三個 7 段顯示器可以顯示的最大值(請參閱上文「參數泛型」部分)。通用 ss_polarity 設定為「0」,表示共陽極。要顯示數字,只需在數字輸入埠上輸入數字即可。此處顯示的數字為「89」。數字經過內部轉換後(需要 10 位元 + 3 個時脈週期),將輸出到 7 段顯示器,如圖所示。第一位數字的前導零未啟用,其對應的輸出設定為關閉:「1111111」。接下來的數字「8」所有段落都打開:「0000000」,最後一位數字「9」只有「e」段關閉:「0000100」。一旦輸入數字變為「123」,該元件將再次執行必要的轉換,並將結果對應到相應的7段輸出。

圖 4. 範例時序圖

重置

reset_n 輸入連接埠必須為邏輯高電平,7 段磁碟機元件才能運作。此連接埠上的邏輯低電平會非同步重置元件。重置期間,組件將清空 7 段顯示器。任何正在進行的內部轉換都將中止。重置解除後,組件立即開始轉換數位輸入訊號,並將結果輸出到 7 段顯示器上。

結論

這款多位 7 段驅動器是一個靈活的可程式邏輯元件,可在適當數量的 7 段顯示器上顯示多位整數。前導零不顯示。7 段顯示器的數量可配置,讓使用者設定組件以適應所需的輸入整數值範圍。7 段顯示器的極性也是可設定的。

相關主題

七段顯示器 Pmod 控制器(VHDL)- 此設計使用本頁所述的多位 7 段顯示磁碟機元件將 FPGA 連接到具有兩個透過共用數據線連接的 7 段顯示器的周邊裝置模組。