程式碼下載

版本 2.0:pwm.vhd (5.1 KB)

工作週期之間的轉換時常從脈衝中心開始,以避免脈衝形狀異常。

版本 1.0:pwm_v1_0.vhd (4.5 KB)

首次公開發布

特點

- PWM 產生器元件的 VHDL 原始碼

- 可配置工作週期解析度

- 可配置每相輸出數目

- 可配置 PWM 頻率

- 圍繞脈衝中心進行調變

- PWM 反向輸出

介紹

本文詳細介紹了一個用於 CPLD 和 FPGA 的脈寬調變(PWM)產生器元件,該元件以 VHDL 語言編寫。此元件根據使用者邏輯設定的工作週期輸出 PWM 訊號。每個脈衝的中心位於 PWM 頻率,脈衝寬度圍繞中心變化。如果設定為多相,則組件將為每個相產生一個 PWM 訊號,間隔均勻。例如,當設定為三相時,它將產生三個相位差 120° 的 PWM 輸出。此元件使用 Quartus II 12.1 版本設計,並使用 ModelSim-Altera 10.1b 進行測試。資源需求取決於具體實現。圖 1 展示了整合到系統中的 PWM 產生器的典型範例。

圖 1. 範例實現

工作原理

系統時脈除以 PWM 頻率等於一個 PWM 週期內的系統時脈數。計數器定義每個相位的 PWM 週期。每個 PWM 相位都有一個計數器,其值隨相位偏移。每個計數器在每個系統時脈週期遞增,並在到達其週期結束時清除。

工作週期決定了 PWM 訊號上升緣和下降緣在週期內出現的點。圖 2 展示了確定這些位置的基本概念。訊號的下降緣發生在工作週期的 1/2 處,而上升緣發生在週期末尾減去 1/2 工作週期的位置。計數器到達每個位置後,PWM 訊號就會進行對應的切換。由於半個工作週期永遠不會超過半個週期,因此下降緣總是發生在上升緣之前。

圖 2. 與 PWM 週期同相的脈衝波形

可配置參數

PWM 產生器使用 ENTITY 中設定的四個 GENERIC 參數進行配置。表 1 列出了這些參數。 PWM 產生器不需要特定的輸入時脈,只要使用者將 sys_clk 參數設定為提供的時脈頻率即可。參數 pwm_freq 對應於 PWM 頻率。bits_resolution 決定脈衝寬度的解析度。例如,值為 8 表示解析度為 8-bit。因此,脈衝寬度的解析度為 28 或 256,因此在這種情況下,最精細的脈衝寬度調整是週期(即 1/ pwm_freq)除以 256。參數 phases 設定輸出數量及其相互關係。PWM 輸出的數量為 phases,且這些輸出彼此之間相差 360°。

表 1. 通用參數

由於 PWM 週期在系統時脈中定義為 sys_clk / pwm_freq,因此此比率也會影響工作週期解析度。如果工作週期解析度超過 PWM 週期內的系統時脈數,則無法實現工作週期解析度。同樣,如果週期不是解析度的整數倍,則實現的工作週期可能會出現單位舍入誤差。

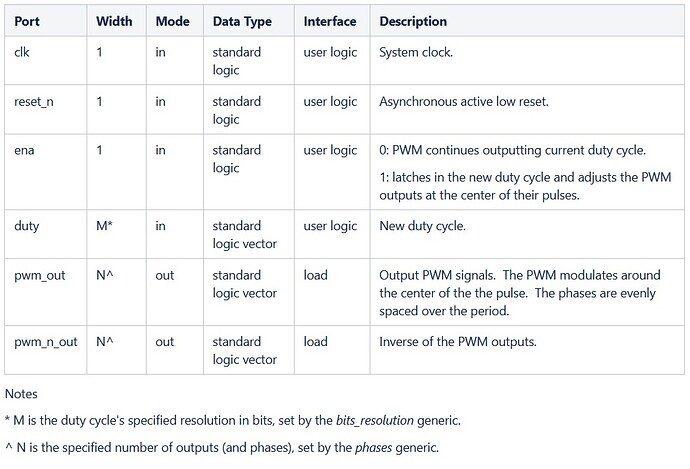

連接埠描述

表 2 列出了 PWM 產生器的連接埠。

表 2. 連接埠描述

控制工作週期

使用者邏輯可以透過在 duty 連接埠閂鎖新的工作週期值來控制工作週期。當 ena 連接埠設定為「1」時,PWM 產生器會在所有系統時脈週期內閂鎖此連接埠的值。圖 3 顯示了 ModelSim 模擬中工作週期的變化過程。請注意,在變更工作週期時,原始脈衝寬度和新脈衝寬度之間會有一個中間寬度的脈衝。這是因為新的工作週期在脈衝中心生效,因此該脈衝的寬度等於舊脈衝寬度的一半加上新脈衝寬度的一半。

圖 3. 改變工作週期的模擬

重置

reset_n 輸入連接埠必須為邏輯高電平,PWM 產生器元件才能運作。此連接埠上的邏輯低電平會非同步重置元件。重置期間,元件會清除週期計數器,並將 PWM 輸出和 PWM 反轉輸出皆設為「0」。

結論

此 PWM 產生器是一款可編程邏輯元件,可產生 PWM 和 PWM 反相輸出。系統時脈、PWM 頻率、工作週期解析度和相數均可配置。使用者邏輯介面可控制 PWM 工作週期。