程式碼下載

DAC DAC121S101 Pmod 控制器(頂層檔案):pmod_dac121S101.vhd (8.3 KB)

具有雙 MOSI 的 SPI 主控(必須包含在專案中):spi_master_dual_mosi.vhd (9.7 KB)

特點

- Digilent Pmod DA2(適用於 TI 的 DAC121S101 數位類比轉換器的 Pmod)精簡介面的 VHDL 原始碼

- 使用簡單的平行介面同時控制 Pmod 的兩個 12-bit DAC

- 處理與 DAC Pmod 的所有串列通訊

- 可設定的系統時脈頻率

介紹

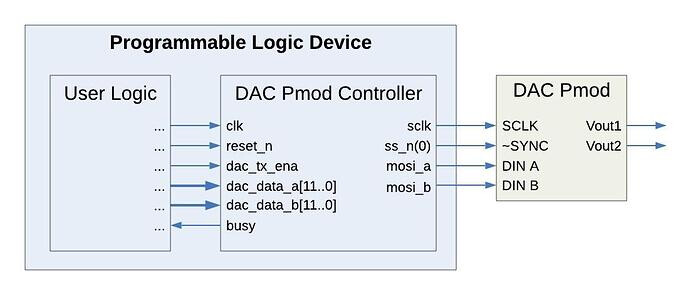

本文詳細介紹了一個 VHDL 元件,負責處理與 Digilent 的 Pmod DA2(用於 DAC121S101)的接口,如圖 1 所示。圖 2 展示了此 DAC Pmod 控制器整合到系統中的典型範例。如圖所示,DAC Pmod 控制器連接到 Pmod 連接埠並執行交易以設定 DAC 輸出。資料被閂鎖在簡單的平行介面上,這些介面可以連接到使用者邏輯或 FPGA 上的輸入連接埠。

圖 1. 用於 DAC121S101 的 Digilent Pmod DA2

圖 2. 範例實現

背景

Pmod DA2 提供兩個 12-bit TI DAC121S101 數位類比轉換器。轉換器使用提供的電源電壓作為電壓基準,並內建支援軌對軌輸出擺幅的晶片上放大器。它們透過最高工作頻率為 30MHz 的串列介面進行控制。

工作原理

DAC Pmod 控制器使用一個簡單的狀態機和一個修改版的 SPI 主控元件來控制 DAC Pmod。

狀態機

此設計使用圖 3 所示的狀態機來實現其操作。啟動後,組件立即進入 start 狀態。它會保持此狀態 100us,以確保 Pmod 有足夠的時間完成上電。然後,它會進入 pause 狀態。在此狀態下,它會確保與 DAC 的兩次傳輸之間至少間隔 20ns。此時,它會解除宣告 busy 訊號,以指示 DAC Pmod 控制器已準備好與 DAC Pmod 進行新的傳輸,並進入 ready 狀態。它會在 ready 狀態下等待,直到 dac_tx_ena 致能訊號被置位,此時它會閂鎖新傳輸的資料並進入send_data 狀態。在此狀態下,它會與 Pmod 執行傳輸,然後返回 pause 狀態。儘管沒有顯示,但隨時重置組件都會使其返回 start 狀態。

圖 3. 狀態圖

SPI 主控

在 send_data 狀態期間,狀態機控制 SPI 主控元件與 Pmod 上的 DAC 進行通訊。本設計中使用的 SPI 主控是此處提供的常用 SPI 主控的修改版本。此修改版本複製了原始版本的 MOSI 邏輯,以提供兩個獨立的 MOSI 輸出(mosi_0 和 mosi_1)。輸出 MOSI 資料分別來自兩個平行輸入 tx_data_0 和 tx_data_1。透過這種方式,SPI 主控可以使用單一 SPI 匯流排同時與兩個獨立的從屬裝置進行獨立資料傳輸。

SPI 主控配置為 CPOL = 0 和 CPHA = 1,以滿足 DAC121S101 轉換器的要求。

配置時脈

此 DAC Pmod 控制器的時脈配置是透過為 ENTITY 中定義的 GENERIC 參數 clk_freq 和 spi_clk_div 分配數值來實現的。clk_freq 參數必須設定為 clk 輸入連接埠提供的系統時脈頻率(以 MHz 為單位)。公式 1 定義了 spi_clk_div 值的計算方法。

當中 fclk 是提供的系統時脈頻率,以 MHz 為單位。

例如,程式碼中指定的預設值為 spi_clk_div = 1。這是因為該組件是使用 50MHz 的系統時脈進行開發和測試的。50/60 = 0.83,向上捨入為 1。任何 clk_freq ≤ 60 MHz 都會導致預設值 spi_clk_div = 1。

公式 2 定義了串列時脈頻率 fsclk,其結果

此計算使串列時脈低於 DAC 的最大額定通訊頻率 30MHz。當輸入時脈頻率(以 MHz 為單位)為 60 的整數倍時,通訊速度最快。

傳輸

DAC Pmod 控制器在其 busy 輸出上指示其可用性。當 busy 訊號為「0」時,控制器已準備好接受要傳送至 DAC Pmod 的傳輸。置位 dac_tx_ena 輸入會閂鎖 dac_data_a 和 dac_data_b 上的目前值。閂鎖後,控制器會置位 busy 訊號,表示傳輸正在進行中,因此目前無法使用。傳輸完成後,控制器會再次置位 busy 訊號,表示已準備好接受另一個要求。

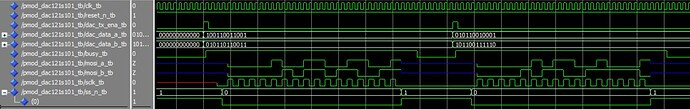

傳輸範例

圖 4 展示了一個傳輸範例。busy 訊號為「0」。然後,使用者邏輯將資料「100110011001」寫入 DAC A,並將「010110110011」寫入 DAC B。控制器置位 busy 訊號,表示請求已閂鎖,此時使用者邏輯可以置位 dac_tx_ena 訊號。控制器將串列通訊傳送到 DAC Pmod,然後在完成後置位 busy 訊號。之後,使用者邏輯發起一個新傳輸,將「010110010001」寫入 DAC A,並將「101100111110」寫入 DAC B。

如果 dac_tx_ena 訊號未置位,則新的傳輸請求將被閂鎖,並在控制器可用後 20ns 內開始。

圖 4. 傳輸範例

連接埠描述

表 1 描述了 DAC Pmod 控制器的連接埠。

表 1. 連接埠描述

連接

此 Pmod 有一個 6 針連接器 J1。表 2 提供了此連接器的引腳排列。DAC Pmod 控制器的連接埠需要指派給連接到此連接器的 FPGA 引腳,具體如下表所示。

表 2. DAC Pmod 引腳排列及與 DAC Pmod 控制器的連接

重置

reset_n 輸入連接埠必須為邏輯高電平,DAC Pmod 控制器元件才能運作。此連接埠上的邏輯低電平會非同步重置元件。重置期間,元件會中止目前與 DAC Pmod 的傳輸,並將 busy 輸出設為高電位以指示其不可用。重置解除後,DAC Pmod 控制器將重新啟動工作。

結論

這款 DAC Pmod 控制器是一款可編程式邏輯元件,可與 Digilent 的 Pmod DA2(用於 DAC121S101 轉換器)介接。它可以根據使用者透過簡單的平行介面提供的輸入,同時控制 Pmod 的兩個轉換器。