特點

適應性單頻訊號提昇器,或稱自適應線路增強器(Adaptive Line Enhancer,簡稱 ALE)是一種有效的學習濾波器,可在高訊噪比(SNR)下降低高斯雜訊。此濾波器會調整濾波器權重,使所需輸入訊號通過,同時降低訊號中的雜訊部分,且在奈奎斯特率(Fs/2)下幾乎無濾波器快速衰減。自適應濾波器可調整自身的頻率響應,從而動態提升濾波器效能。本設計將涵蓋以下主題:

- ALE 濾波器架構設計基礎

- 濾波器穩定性取決於學習系數,mu

- 濾波器縮放以實現更有效率的實現

- 自訂 VHDL 元件設計和實例化,包含 18-bit CODEC 控制器和 ALE 濾波器

- 濾波器特性與驗證

介紹

本參考設計採用 AMD(Xilinx) Spartan 6 開發板和 TI 的 LM4550 ac97 音訊編解碼器。設計基於 Xilinx ISE ver13.1 開發。本設計使用了音訊編解碼器,但並非必要。AMD(Xilinx) Spartan 6 FPGA 整合了 DSP48A1 區塊,是 DSP 邏輯電路設計的理想選擇。整合的 DSP 區塊支援平行數學電路,從而構成能夠進行超快速資料處理的濾波器。只要具備足夠的硬體乘法器(考慮到濾波器的字長),ALE 即可與任何 FPGA 搭配使用。本濾波器實作使用了 58 個 Spartan 6 XC6SLX45 DSP48A1 區塊中的 48 個;具有更多 DSP 區塊的 FPGA 可以支援更多 ALE 接頭,從而提高效能。

背景

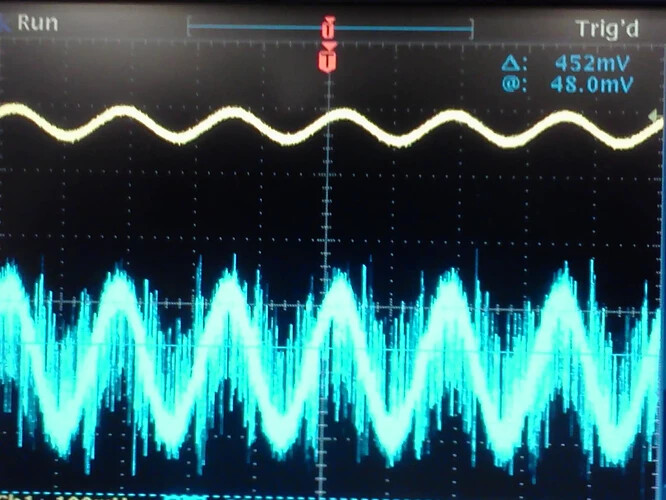

本模組的使用者無需完全理解 ALE 濾波器的設計,但如果了解其基本設計原理,將有助於解決濾波器故障。本背景部分涵蓋了 ALE 濾波器和 VHDL 模組設計本身的基礎知識。此設計使用內部高斯雜訊產生器,其中左聲道在濾波器之前和雜訊之後路由訊號,右聲道是濾波器之後的路徑,在此雜訊被大大降低。濾波器對「雜訊 + 訊號」和「降低的雜訊 + 訊號」的影響如下圖 1 和圖 2 所示。

圖 1 –「雜訊 + 訊號」(藍色)和「降低雜訊 + 訊號」(黃色)

圖 2 –「雜訊 + 訊號增加」(藍色)和「雜訊 + 訊號減少」(黃色)

ALE 也使用任意波形產生器的外部雜訊源進行了測試。如下圖 3 所示。

圖 3 – 「外部雜訊 + 訊號」(黃色)和「降低雜訊 + 訊號」(藍色)

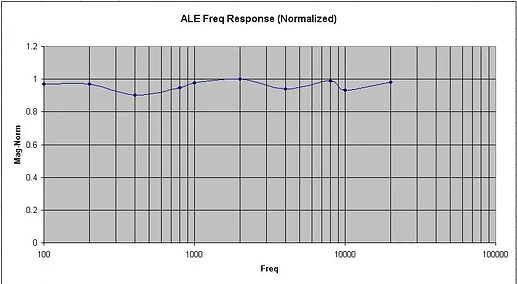

自適應濾波器在濾波訊號時表現出色,特別適用於條件變化、寬頻雜訊與窄頻訊號頻譜重疊,以及雜訊源未知或變化劇烈的應用。濾波器透過改變權重來降低雜訊並最大化相關訊號輸出。ALE 的頻率響應繪製於下圖 4 。請注意,在 24KHz 的奈奎斯特頻率範圍內,沒有任何明顯的衰減。

圖 4 – ALE 頻率響應至奈奎斯特頻率

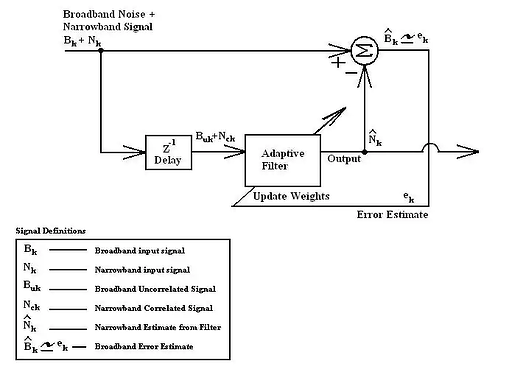

輸入訊號(B(k) + N(k))延遲一個樣本,以使寬頻雜訊訊號與其本身訊號去相關(de-correlate),從而得到( Bu(k) + Nc(k) )。這是因為雜訊是隨機的,相位的微小變化會使訊號去相關。請注意,窄頻訊號 Nc(k) 與 N(k) 保持相關,因為它不是隨機的,而是具有很大的週期性和爭議性。訊號流程圖如下圖 5 所示。

圖 5 – ALE 訊號流程圖

ALE 濾波器的工作原理是將濾波器權重初始化為任意值,並在每個取樣週期內進行調整。這透過計算濾波器輸出 N-hat-k 來實現,具體計算公式 1 如下。此窄頻訊號(N-hat-k)用於計算誤差估計值(ek),具體計算公式 2 如下。 ALE 採用最小平方法誤差代價函數來尋找最佳濾波器權重,從而估計訊號輸出。ALE 並非使用拋物線均方誤差代價函數中梯度向量的期望值,而是將目前輸入 FIFO 值(瞬時梯度)乘以學習系數 (mu)。這透過使用最小均方近似來調整權重;使用下面的公式 3 進行最大下降。下降沿著 n 維拋物線結構向下移動,維度由濾波器的階數決定。當梯度為零時,最小均方誤差已最大程度地減少。為了避免過度調整,我們採用由學習系數 mu 決定的小步長。mu 值使用下方公式 4 進行選擇。此 mu 值決定了濾波器值在給定取樣週期內的變化量。選擇一個 mu 值非常方便,可以方便地對誤差估計值與 FIFO 值的乘積進行桶形移位,但同時,也需要保持 mu 足夠小,以避免偏離 n 維拋物線的誤差曲面。下圖 6 顯示了具有兩個權重的均方誤差曲面的簡化表示。

公式 1

公式 2 ![]()

公式 3

公式 4

圖 6 – 均方誤差曲面的簡化表示

應用

電路建構

ALE 濾波器模組採用以下流程:

- 16bit 深 x 18bit 移位暫存器,用於移入樣本

- 狀態更新,用於時序和標誌控制

- 16bit 線性回授移位暫存器,用於截斷期間的抖動

- 依賴定時器的進程,用於控制資料路徑標誌

- 16 項平行乘法器流程

- 輸出項的截斷和顫化過程

- 作為卷積的一部分的大型加法器樹

- 回授減法進程

- 誤差估計區塊

- 回授截斷與顫化過程

- 濾波器接頭調整流程

- 32-bit 至18-bit 截斷區塊,用於輸出至 DAC

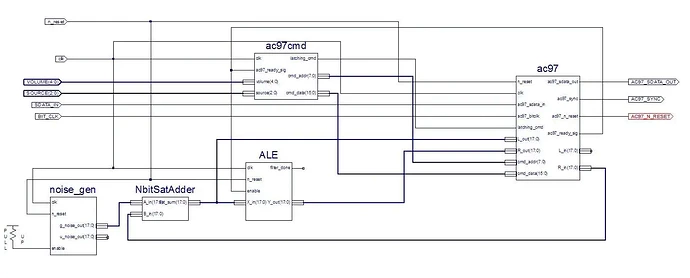

ALE 架構如下圖 7 所示。

圖 7 – ALE 濾波器架構

ALE 濾波器模組實例化

ALE 濾波器的實例化非常簡單,只需將 ALE.vhd 檔案添加到專案中,然後在 Xilinx ISE 中對應頂層端口,或使用原理圖檔案連接到端口即可。在「processes」標籤中建立原理圖符號後,即可在原理圖編輯器中新增線路來連接到連接埠。頂層原理圖如下圖 8 所示。在硬體中驗證模組時,必須在電路板上手動重設 noise_gen.vhd 模組,以便為偽隨機數產生器提供種子。

圖 8 – Xilinx ISE 原理圖頂層

此應用以 100MHz 的頻率運行,並預留了足夠的間隙以適應更快的速度。

硬體測試與驗證

本模組透過使用 AMD(Xilinx) 的模擬軟體 ISim 進行了全面測試。一個基本的定時器驅動狀態機控制致能標示,用於同步數學運算、截斷和顫化中間運算以及在每個採樣週期閂鎖輸出。每個採樣週期都會推進延遲線並啟動標示狀態機。該模組也在硬體上進行了驗證,如上圖 1 至圖 3 所示。

設計軟體

本參考設計採用 Xilinx Spartan 6 開發板和 TI 的 LM4550 ac97 音訊編解碼器。設計基於 Xilinx ISE ver13.1 開發。本設計無需音訊編解碼器。此設計可擴展至眾多非音訊應用,取樣率不僅限於 48KHz。

總結

自適應濾波器在濾波訊號方面表現出色,尤其適用於條件變化、寬頻雜訊與窄頻訊號頻譜重疊,以及雜訊源未知或變化劇烈的應用。本設計針對音訊應用進行了測試,但可以縮小設計規模,以實現速度更快、解析度更低的濾波器。此外,本文也介紹了 ALE VHDL 模組濾波器設計的基礎知識。

附加資訊

AC97 編解碼器驅動程式、NbitSatAdder 和 noise_gen 模組在另一文章「使用 VHDL 的 N-Bit 飽和數學進位預看組合加法器設計」中有更詳細的介紹。更多 DSP 主題和濾波器設計訊息,請參考以下書籍:《Digital Signal Processing, A Practical Approach》(作者:Emmanuel C. Ifeachor 和 Barrie W. Jervis)。

附錄:下載

完整的 Lattice Diamond 專案可在此處下載。

ALE.vhd (24.6 KB)

noise_gen.vhd (11.3 KB)

NbitSatAdder.vhd (3.0 KB)

ac97.vhd (7.6 KB)

ac97cmd.vhd (4.3 KB)