特點

無限脈衝響應濾波器(Infinite Impulse Response Filters,簡稱 IIR) 可用於從音訊到資料處理等眾多應用,而且處理器成本低。一個雙二階濾波器單元在 FPGA 中僅需 5 個(18-bit)乘法器,如果需要 32-bit 字長,則最多可佔用 20 個。本文將涵蓋以下設計主題:

- IIR 濾波器雙二階濾波器單元設計基礎知識

- 濾波器穩定性和 Z 傳遞函數

- 以 Excel 為基礎的雙線性 Z 變換 IIR 設計工具

- 濾波器縮放以實現更有效率的實現

- 濾波器特性與驗證

- 自訂 VHDL 元件設計和實例化,包含 18-bit CODEC 控制器以及 18-bit 和 36-bit IIR 雙二階濾波器單元

介紹

此參考設計採用了 AMD(Xilinx) Spartan 6 開發板 和 TI 的 LM4550 音訊編解碼器。設計基於 Xilinx ISE ver13.1 開發。該設計採用了音訊編解碼器,但感測器數據也可以被過濾,因此編解碼器並非必要。IIR 濾波器也能很好地濾波感測器資料。此濾波器可以縮小到更小的字長,因此可以將其作為重新設計自訂 IIR 濾波器的起點,以加快實現速度。AMD(Xilinx) Spartan 6 FPGA 整合了 DSP48A1 區塊,是 DSP 邏輯電路設計的理想選擇。整合的 DSP 區塊支援平行數學電路,從而實現能夠超快速處理資料的濾波器。IIR 濾波器在前授和回授路徑中使用了 32x32 和 32x18 位元乘法器以及多個加法器。只要有足夠的硬體乘法器,並且考慮到濾波器的字長,IIR 濾波器就可以與任何 FPGA 一起使用。

背景

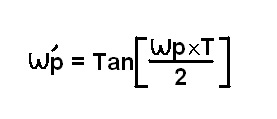

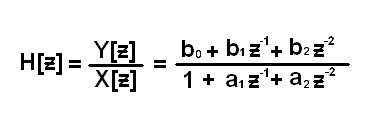

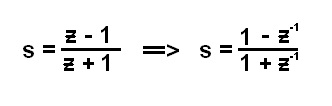

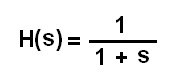

本模組的使用者無需完全理解 IIR 濾波器的設計,但如果理解其基本設計原理,將有助於解決濾波器故障。本背景部分涵蓋了 IIR 濾波器設計的基礎知識,包括雙線性 z 變換和 VHDL 模組設計本身。IIR 濾波器是一種基於類比傳遞函數原型設計的遞迴濾波器。雙線性 z 變換是一種線性近似,它將 s 域傳遞函數對應到離散 z 域。在此過程中,jw(j-omega) 軸透過奈奎斯特取樣率 Fs/2 的頻率彎曲對應到單位圓。彎曲關係如下面的公式 1 所示。然後,s 域(公式 2)可以轉換到 z 域,其中「z^-1」是延遲運算子。雙二次函數只是兩條延遲線;一條是前授路徑,另一條是回授路徑。z 傳遞函數如下面的公式 3 所示。雙二次框圖如下圖 1 所示。

公式 1

公式 2

公式 3

圖 1 – 雙二次訊號流方塊圖

回授路徑可能導致濾波器不穩定。在 s 域中,如果極點位於左半平面,則濾波器被認為是穩定的;這些極點將對應到 z 域中單位圓內的區域。下圖 2 展示了 j-omega 軸在單位圓上的對應。

圖 2 – S 到 Z 平面的對應

由於從 s 平面到 z 平面的對應,頻率發生了扭曲。它們本質上與 z 平面(與 s 平面相關)聚集在一起,其函數關係如上公式 1 所示。j-ω 軸的兩端在 z 平面上相交於 π 弧度,這也恰好是取樣頻率的一半。透過求解上二次方程式和下二次方程式(找到極點和根)並將其繪製在 z 平面內,可以判斷濾波器是否固有穩定。如果複向量的振幅小於 1,則它位於單位圓內。這意味著可以預期濾波器是穩定的。這是因為左半 s 平面直接對應到 z 平面的單位圓內。

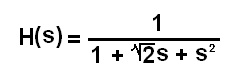

使用雙線性 z 變換推論出適當雙二次系數的第一步是從模擬原型開始。在 Excel 工具中,低通二階巴特沃斯(Butterworth)原型用於計算低通和高通濾波器系數,如下公式 4 示。帶通和帶阻原型則使用公式 5。

公式 4

公式 5

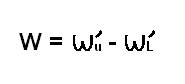

接下來,需要使用公式 6、7、8 或 9 中的變換之一對模擬原型的傳遞函數進行反歸一化。具體方法是將模擬原型中的「s」替換為以下變換之一。低通到低通和低通到高通的變換用於二階原型。低通到帶通和低通到帶阻的變換用於一階原型。請注意,ω 質數項來自上述公式 1 中的頻率彎曲函數。

公式 6

公式 7

公式 8

公式 9

帶通函數和帶阻函數新增了兩個項,它們可以在下面的公式 10 和 11 中找到。這兩個項目來自我們想要創建的濾波器的頻率彎曲頻寬。完成所有代數運算後,可以透過在公式 12 中代入 s 來應用最終的 z 變換。使用一些代數運算,將 z 傳遞函數的頂部和底部乘以 z 的最高負階,即可獲得類似於上面公式 3 中的雙二次傳遞函數。

公式 10

公式 11

公式 12

這些值也可以使用附件的 Excel 工具或您常用的科學計算程式來取得。找到系數後,只需將值轉換為二進位有符號定點「2.30」格式即可。這意味著最高兩位有效數字的值介於 -2 到 1 之間,其餘 30 位元為正小數部分。範例可在下一節中找到。

應用

電路建構

- IIR 濾波器模組使用以下組件:

- 3-bit 計數器,用於啟用標誌同步

- 5 個 32-bit IIR 系數暫存器

- 2 條 2 級延遲線(前饋和回饋)

- 2 狀態, 狀態機,用於同步數學運算

- 20/10 平行乘法器(32 x 32-bit/32 x 18-bit)

- 64-bit 轉 32-bit 和 50-bit 轉 18-bit 截斷區塊(32 x 32 位元/32 x 18 位元)

- 求和級,一個時脈週期內執行兩次加法和兩次減法

- 32-bit 轉 18-bit 截斷區塊,用於輸出至 DAC

實例化 IIR_Biquad.vhd 濾波器模組

IIR 濾波器的實例化非常簡單,只需將 IIR_Biqhad_xx.vhd 檔案加在專案中,然後在 AMD(Xilinx) ISE 中對應頂層端口,或使用原理圖檔案連接到端口即可。在「流程」標籤中建立原理圖符號後,即可在原理圖編輯器中新增連線來連接至連接埠。頂層原理圖如下圖 3 所示。

圖 3 – AMD(Xilinx) ISE 原理圖頂層

此應用程式以 100MHz 運行,並預留了足夠空間以支援更快的運行速度。系數的選擇方式多種多樣,包括科學計算程序、使用極點零點放置法、匹配 z 變換以及最常用的雙線性 z 變換近似法(如上文背景部分所示)的人手計算。其中包含一個 Excel 文件,該文件使用雙線性 z 變換產生低通、高通、帶通和帶阻 IIR 濾波器的雙二次系數。系數計算完成後,需要將其轉換為二進位有符號定點格式「2.30」。這將產生介於 -2 到 1.999999999068677 之間的數字…

只需將小數部分乘以 2^30,然後將整數部分輸入到能夠轉換大數值的二進制數的計算器中,然後進行轉換即可。轉換後的部分將是系數的小數部分。接下來,只需找出 -2 到 1 之間的整數部分即可。若系數為負,則求 2 減去系數。這樣就得到了正數部分(小數部分),將其與最高有效位元 (-2) 相加,就得到了我們想要的原始負系數。此轉換的範例如下圖 4 和圖 5 所示。

圖 4 – 二進位有符號定點數 2.30 轉換範例 1

系數通常為負數,如果需要負系數,請參考下圖 5 中的轉換範例。

圖 5 – 二進位有符號定點 2.30 轉換範例 2

系數轉換完成後,將其替換為 IIR_Biquad VHDL 模組中現有的系數,然後進行綜合和測試。

硬體測試與驗證

此模組已使用AMD(Xilinx) 的模擬軟體 ISim 進行了全面測試。一個基本的定時器驅動雙態狀態機控制啟用標誌,用於同步數學運算、截斷中間運算以及在每個取樣週期閂鎖輸出。每個取樣週期都會推進延遲線並啟動標誌狀態機。每個測試都在 ISim 中進行了測試。ISim 模擬螢幕截圖如下圖 6 所示。

圖 6 – ISim 模擬截圖

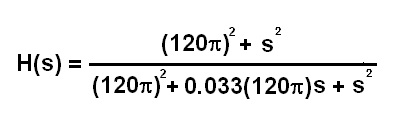

硬體測試採用 LM4550 音訊編解碼器。我們創建並測試了多個濾波器,方法是引入 0 至 24kHz 的 18-bit 有衝突訊號和一個單脈衝,以獲得濾波器的脈衝響應。然後對脈衝響應進行快速傅立葉變換,以獲得濾波器的頻率響應。創建的第一個濾波器是 60Hz 二階 IIR 巴特沃斯陷波濾波器。我們還創建了一個類比濾波器,即 60Hz 雙 T 型陷波濾波器,用於與數位實現進行比較和對比。由於嚴格的約束,數位 IIR 濾波器實現自然會受到較大的群延遲影響。類比和 IIR 數位濾波器的頻譜輸出如下圖 7 和圖 8 所示。兩個濾波器的阻帶衰減都遠低於背景雜訊。如果使用更大的輸入測試訊號,則可以實現更大的衰減。

圖 7 – 60 Hz 類比雙 T 型陷波濾波器

圖 8 – 60 Hz 數位 IIR 巴特沃斯陷波

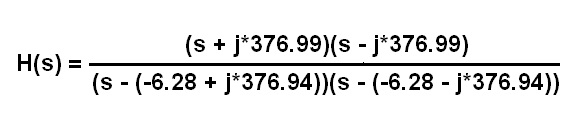

由於設計所需的分立元件,模擬濾波器存在熱漂移和頻率缺陷。數位 IIR 濾波器的中心頻率似乎恰好對準,在直流側有少量衰減。每個濾波器的 s 域和 z 域傳遞函數分別如下式 13 和 14 所示。

公式 13

公式 14

我們可以透過求解分子和分母的二次方程式來確定零點和極點的位置。在這種情況下,兩者都是複數,如下公式 15 和 16 所示。

公式 15

公式 16

模擬和 IIR 陷波濾波器的極點/零點圖如下圖 9 所示。請注意,在兩種實作中,濾波器都處於穩定邊緣。

圖 9 – 類比和 IIR 陷波濾波器實現的極點/零點圖

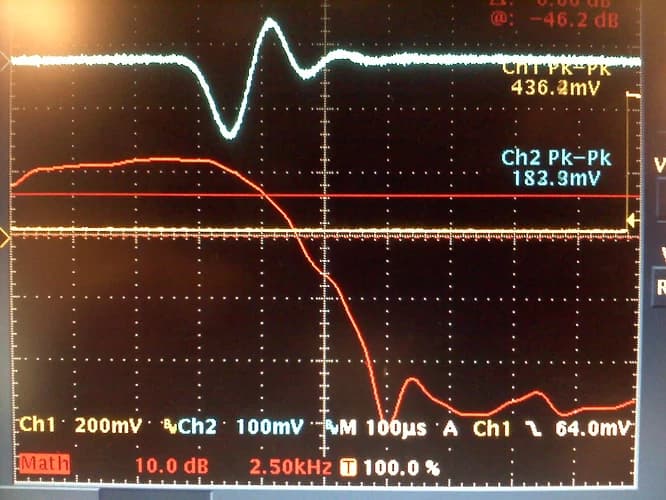

下方是幾個示波器範例截圖。這些測試向濾波器引入了一個脈衝。脈衝響應(藍色部分)隨後在示波器上進行 FFT 運算;濾波器的頻率響應(紅色部分)則以紅色重建。下圖 10 所示的是一個 Q 值較大的 7KHz 帶通濾波器。

圖 10 – 7KHz,帶通實現

下圖 11 所示為基於二階巴特沃斯濾波器的帶阻濾波器。

圖 11 – 2.7KHz, 帶阻濾波器實現

圖 12 提供了另一個 IIR 實作方案。此濾波器採用 3 個雙二次切比雪夫(Chebyshev)濾波器段串接,以獲得更大的阻帶衰減和更小的過渡帶。

圖 12 – 8KHz, 低通切比雪夫 IIR 實現

功能、限制和修改

本參考設計採用 AMD(Xilinx) Spartan 6 開發板與 TI 的 LM4550 音訊編解碼器。設計採用 Xilinx ISE ver13.1 開發。本設計中無需音訊編解碼器。該設計可擴展到許多非音訊應用,而不僅限於 48KHz 取樣率。

總結

本參考設計示範如何使用嵌入式 IIR 濾波器以及雙二階系數計算工具,在 FPGA 中快速濾波資料流。本設計主要針對音訊應用進行測試,但可縮小設計規模,以實現速度更快、解析度更低的濾波器。此外,本文也涵蓋了 IIR 濾波器設計的基礎知識。

補充資料

更多 DSP 主題和濾波器設計訊息,請參閱線上書籍:《The Scientist and Engineer’s Guide to Digital Signal Processing》, DR, Steven W. Smith。 http://www.dspguide.com

附錄:下載

完整的 VHDL IIR 濾波器設計(適用於 18bit/48KHz 音訊訊號)VHDL 檔案和 Excel IIR 設計工具可在此處下載。

IIR_Filter_Coef_Generator.xls (33 KB)

IIR_Biquad.zip (2.1 MB)