程式碼下載

PS/2 鍵盤介面邏輯:ps2_keyboard.vhd (5.1 KB)

解彈跳邏輯(必須包含在項目中):debounce.vhd (2.4 KB)

特點

- PS/2 鍵盤介面的 VHDL 原始碼

- 輸出從鍵盤接收的 PS/2 通斷程式碼

- 當有新程式碼可用時設定標示輸出

- 驗證 PS/2 傳輸的同位、起始和停止位元

- 可設定的系統時脈頻率

- 在 PS/2 和系統時脈域之間同步

- 對傳入的 PS/2 訊號進行解彈跳

介紹

本文詳細介紹了一個用於 CPLD 和 FPGA 的 PS/2 鍵盤介面組件,該組件以 VHDL 編寫。此元件接收來自 PS/2 鍵盤的資料傳輸,並透過平行介面向使用者邏輯提供鍵盤的通斷程式碼。此組件使用 Quartus II 12.1 版設計。圖 1 展示了一個整合到系統中的 PS/2 鍵盤介面的典型範例。這裡提供了一個範例設計,該範例設計實現了該 PS/2 鍵盤介面組件,用於實現 PS/2 鍵盤到 ASCII 的轉換器。 PS/2 鍵盤介面本身是此處提供的 PS/2 主機收發器的簡化版本。

圖 1. 範例實現

背景

PS/2(IBM 個人系統/2)是一種透過 6 針 Mini-DIN 連接器將鍵盤和滑鼠連接到 PC 相容電腦系統的介面。計算系統必須為鍵盤或滑鼠提供 5V 電源和接地連接。通訊透過兩線串列介面進行,該介面由一條時脈線和一條數據線組成。兩條線都需要上拉電阻(圖 1 所示的電阻為 2kohm)。圖 1 中的 120ohm 串聯電阻用於將 3.3V FPGA I/O 連接到 5V 訊號。

通電後,鍵盤會進行自初始化序列。初始化完成後,鍵盤即可透過 PS/2 介面傳輸鍵盤事件。

圖 2 展示了傳輸格式。非活動狀態時,時脈和資料訊號均為邏輯高電位。鍵盤同時提供時脈和數據。時脈頻率在 10kHz 至 16.7kHz 之間(即週期為 60-100us)。資料以起始位元(邏輯低電位)開始,接著是一個資料位元組、一個同位位元,最後是一個停止位元(邏輯高電位)。資料以 LSB 優先發送。每個位元應在時脈訊號的下降緣讀取。完成後,時脈和資料訊號均恢復至邏輯高電位。

圖 2. PS/2 鍵盤傳輸時序圖

資料位元組代表鍵盤掃描碼的一部分:通碼(按下按鍵)或斷碼(釋放按鍵)其中一個。掃描碼有三種不同的設置,但絕大多數鍵盤使用附錄中提供的掃描碼集2。通碼通常由一個或兩個位元組組成。如果通碼使用兩個字節,則第一個位元組為 x“E0”。給定按鍵的斷碼通常與其通碼相同,但斷碼會包含一個額外的 x“F0”位元組作為倒數第二個位元組(PAUSE 和 PRNT SCRN 鍵除外)。

雖然可以向鍵盤發送資料(例如更改其設定等),但這通常是不必要的,並且不包含在此 VHDL 元件中。但是,可以使用此處提供的 PS/2 主機收發器元件來執行此操作。

工作原理

圖 3 概念性地展示了 PS/2 鍵盤介面組件的架構。首先對來自鍵盤的時脈和資料訊號進行同步和解彈跳處理(解彈跳組件的 VHDL 程式碼及相關文件可在此處取得)。隨後,產生的內部 PS/2 資料訊號在 PS/2 時脈的下降緣以串列方式載入到移位暫存器中。空閒計數器用於確定傳輸何時完成,完成時間定義為 PS/2 時脈保持高邏輯電平的時間超過 55us,即超過最壞情況下 PS/2 時脈週期的一半。組合誤差校驗邏輯用於驗證資料的起始位元、停止位元和同位位元。當 PS/2 連接埠空閒且資料有效時,該元件將輸出接收到的 PS/2 編碼,並將 ps2_code_new 訊號設為高電平,以指示 ps2_code 匯流排上有新的可用編碼。該程式碼將保留在匯流排上,直到接收到新的編代碼。 ps2_code_new 訊號保持高電平直到另一個 PS/2 傳輸開始(當低 PS/2 時脈訊號清除空閒計數器時)。

圖 3. PS/2 鍵盤介面邏輯架構

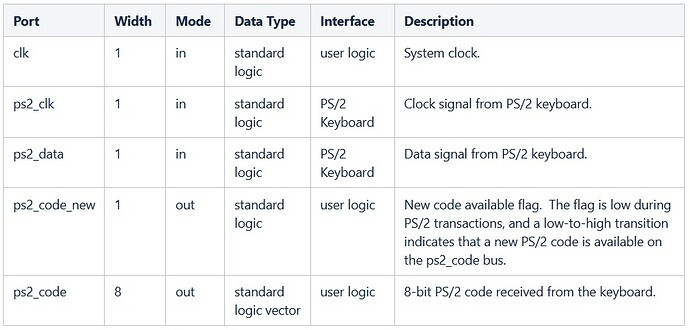

連接埠描述

表 1 描述了 PS/2 鍵盤介面的連接埠。

表 1. 連接埠描述

設定時序參數

系統時脈速度會影響解彈跳時間和空閒計數器的時序。為了確保元件正常運行,必須正確設定 ENTITY 中宣告的兩個 GENERIC 參數 clk_freq 和 debounce_counter_size。clk_freq 參數必須設定為系統時脈頻率(以 Hz 為單位)。所提供程式碼中的預設設定為 50MHz(元件模擬和測試的頻率)。debounce_counter_size 參數必須設定為 2^debounce_counter_size / clk_freq = 5us,具體設定請參閱此處的解彈跳元件文件。對於 50MHz 系統時脈,debounce_counter_size = 8。

範例傳輸

圖 4 顯示了範例傳輸的時序圖。PS/2 時脈訊號變成低電位後,ps2_code_new 標示解除宣告,表示新的 PS/2 鍵盤傳輸正在進行中。傳輸完成後,ps2_code_new 標示宣告,表示新的 PS/2 編碼已收到,並且可在 ps2_code 匯流排上使用。在本例中,收到的 PS/2 編碼為 x“1C”,即「A」鍵的產生編碼。

圖 4. PS/2 傳輸範例

總結

此 PS/2 鍵盤介面是一個可編程邏輯元件,用於接收來自 PS/2 鍵盤的傳輸。它同步時脈域、解消輸入訊號彈跳、執行錯誤檢查,並在其平行輸出匯流排上出現新的鍵盤程式碼時通知使用者邏輯。

附錄:掃描碼集 2

| Key | Make Code | Break Code |

|---|---|---|

| A | 1C | F0,1C |

| B | 32 | F0,32 |

| C | 21 | F0,21 |

| D | 23 | F0,23 |

| E | 24 | F0,24 |

| F | 2B | F0,2B |

| G | 34 | F0,34 |

| H | 33 | F0,33 |

| I | 43 | F0,43 |

| J | 3B | F0,3B |

| K | 42 | F0,42 |

| L | 4B | F0,4B |

| M | 3A | F0,3A |

| N | 31 | F0,31 |

| O | 44 | F0,44 |

| P | 4D | F0,4D |

| Q | 15 | F0,15 |

| R | 2D | F0,2D |

| S | 1B | F0,1B |

| T | 2C | F0,2C |

| U | 3C | F0,3C |

| V | 2A | F0,2A |

| W | 1D | F0,1D |

| X | 22 | F0,22 |

| Y | 35 | F0,35 |

| Z | 1A | F0,1A |

| 0 | 45 | F0,45 |

| 1 | 16 | F0,16 |

| 2 | 1E | F0,1E |

| 3 | 26 | F0,26 |

| 4 | 25 | F0,25 |

| 5 | 2E | F0,2E |

| 6 | 36 | F0,36 |

| 7 | 3D | F0,3D |

| 8 | 3E | F0,3E |

| 9 | 46 | F0,46 |

| ` | 0E | F0,0E |

| - | 4E | F0,4E |

| = | 55 | FO,55 |

| |5D | F0,5D | |

| BKSP | 66 | F0,66 |

| SPACE | 29 | F0,29 |

| TAB | 0D | F0,0D |

| CAPS | 58 | F0,58 |

| L SHFT | 12 | FO,12 |

| L CTRL | 14 | FO,14 |

| L GUI | E0,1F | E0,F0,1F |

| L ALT | 11 | F0,11 |

| R SHFT | 59 | F0,59 |

| R CTRL | E0,14 | E0,F0,14 |

| R GUI | E0,27 | E0,F0,27 |

| R ALT | E0,11 | E0,F0,11 |

| APPS | E0,2F | E0,F0,2F |

| ENTER | 5A | F0,5A |

| ESC | 76 | F0,76 |

| F1 | 5 | F0,05 |

| F2 | 6 | F0,06 |

| F3 | 4 | F0,04 |

| F4 | 0C | F0,0C |

| F5 | 3 | F0,03 |

| F6 | 0B | F0,0B |

| F7 | 83 | F0,83 |

| F8 | 0A | F0,0A |

| F9 | 1 | F0,01 |

| F10 | 9 | F0,09 |

| F11 | 78 | F0,78 |

| F12 | 7 | F0,07 |

| PRNT SCRN | E0,12,E0,7C | E0,F0,7C,E0,F0,12 |

| SCROLL | 7E | F0,7E |

| PAUSE | E1,14,77,E1,F0,14,F0,77 | -NONE- |

| [ | 54 | FO,54 |

| INSERT | E0,70 | E0,F0,70 |

| HOME | E0,6C | E0,F0,6C |

| PG UP | E0,7D | E0,F0,7D |

| DELETE | E0,71 | E0,F0,71 |

| END | E0,69 | E0,F0,69 |

| PG DN | E0,7A | E0,F0,7A |

| U ARROW | E0,75 | E0,F0,75 |

| L ARROW | E0,6B | E0,F0,6B |

| D ARROW | E0,72 | E0,F0,72 |

| R ARROW | E0,74 | E0,F0,74 |

| NUM | 77 | F0,77 |

| KP / | E0,4A | E0,F0,4A |

| KP * | 7C | F0,7C |

| KP - | 7B | F0,7B |

| KP + | 79 | F0,79 |

| KP EN | E0,5A | E0,F0,5A |

| KP . | 71 | F0,71 |

| KP 0 | 70 | F0,70 |

| KP 1 | 69 | F0,69 |

| KP 2 | 72 | F0,72 |

| KP 3 | 7A | F0,7A |

| KP 4 | 6B | F0,6B |

| KP 5 | 73 | F0,73 |

| KP 6 | 74 | F0,74 |

| KP 7 | 6C | F0,6C |

| KP 8 | 75 | F0,75 |

| KP 9 | 7D | F0,7D |

| ] | 5B | F0,5B |

| ; | 4C | F0,4C |

| ’ | 52 | F0,52 |

| , | 41 | F0,41 |

| . | 49 | F0,49 |

| / | 4A | F0,4A |

表 A1. 鍵盤掃描碼集 2