Sichern Sie Ihre Zukunft mit einem Microchip FPGA Baustein anstelle des Spartan®-6 von Xilinx

Ist Ihr Umsatz in Gefahr und haben Sie Geschäftseinbußen zu verzeichnen, weil Sie Ihre elektronischen Bauteile nicht bekommen? Leider befinden Sie sich in guter Gesellschaft mit vielen anderen Anwendern.

Ich hatte in letzter Zeit mehrere Gespräche mit FPGA-Anwendern, die ihre Designs auf Bausteinen von Wettbewerbern, wie z.B. der Spartan®-6 LX Serie von Xilinx Inc., entwickelt haben und nun mit einem sofortigen Lieferstopp konfrontiert sind. Es gibt überhaupt keine Bausteine mehr und Redesign-Optionen, die dazu führen, daß entweder sehr große Bausteine verwendet werden, man sich um einen Boot-Prozeß eines Prozessors kümmern muß oder eine Migration auf ein neues Tool erzwungen wird. Selbst dann kann es sein, daß Sie sich nur ein paar zusätzliche Jahre der Verfügbarkeit erkaufen.

Wie wäre es, wenn Sie Ihre Zukunft wirklich schützen und ein FPGA wählen, das:

– mit geringem Migrationsaufwand verbunden ist

– ohne End-of-Life-Praxis verfügbar ist

Dies ist der perfekte Zeitpunkt, um eine absolute Krise in eine Chance zu verwandeln, und Microchip ist bereit, Ihnen dabei zu helfen, wieder in Gang zu kommen. Genau wie bei den Anwendern, mit denen ich gesprochen habe- Meist ist geplant, daß sie innerhalb eines halben Jahres wieder in Produktion gehen können.

In diesem Artikel zeige ich Ihnen einen Entscheidungsbaum für die Auswahl eines geeigneten Microchip FPGAs, wie man das bestehende Design aus der Software-Perspektive migriert und einige wichtige Unterschiede und Gemeinsamkeiten zwischen Spartan-6 und den ausgewählten Microchip FPGAs.

Migrations-Entscheidung

Die unmittelbare Frage bei jeder Migration ist aus meiner Sicht die Bewertung des “ob”, “was dann” und “wie”. Für Spartan-6 kursieren einige Wege innerhalb der Bausteine, z.B. der Blog von Adam Taylor, Embedded Systems Consultant, Professor of Embedded System at Innovator Sheffield Hallam University, Author of the MicroZed Chronicles, Arm Innovator. Adam hat einen gültigen Entscheidungsbaum, der jedoch vollständig innerhalb der Xilinx-Bausteine bleibt, was zwar „natürlich“ erscheinen mag, aber Ihre Möglichkeiten einschränkt. Außerdem landet man entweder bei FPGAs mit 100.000 oder 200.000 Logikzellen (Artix-7 100T und 200T), die von ISE unterstützt werden, bei einem neuen Tool, Vivado und seinem eigenen Design-Flow oder bei Zynq® UltraScale+™ MPSoC, bei denen man den Boot-Prozeß als wesentlichen Teil des FPGA-Aufbaus durchführen muß. Und bei diesem Schritt ist ein umfassendes Redesign erforderlich, weg von einer buszentrierten MHS-Datei basiert hin zu einem blockdiagrammbasierten Ansatz.

Ein alternativer Entscheidungsbaum, der Sie in eine Welt praktisch ohne Abkündigungen führt, ist der folgende:

Ich beginne mit dem Entscheidungspunkt, an dem Sie sich für einen Wechsel zu Microchip entscheiden. Je nach Ihrer Erfahrung und Ihrem Entwicklungs-Know-how kann ein Mikrocontroller geeignet sein, der zum Zeitpunkt der Entwicklung des ursprünglichen Projekts noch nicht verfügbar war. Da mein Fokus auf FPGAs liegt, werde ich dieses Thema aber nicht vertiefen.

Der nächste Schritt besteht hauptsächlich darin, die Hauptarchitektur zu bestimmen. Wenn Ihr Design “größer” ist, können Sie während der Migration einige zusätzliche Vorteile erzielen. Wenn Sie jedoch sofort ein Redesign benötigen, weil Ihre Produktionslinie stillsteht, dann ist der rechte Zweig für Sie genau richtig.

Ein häufiger Anwendungsfall in FPGA-Designs ist die Verwendung von Softprozessoren, wie MicroBlaze. Wenn Ihr Design einen (oder vielleicht mehrere) dieser Prozessoren enthält, haben Sie die Wahl, entweder auf einen Soft-RISC-V oder einen Soft-ARM Cortex M1 für PolarFire™ FPGA zu migrieren oder den in Hardware integrierten Quad-Core RISC-V in PolarFire™ SoC zu verwenden. Ja, dies ergibt einen signifikanten Leistungszuwachs und es ist Ihre Entscheidung, ob Sie diesen Zuwachs wünschen und/oder benötigen.

Für einen sofortigen “1:1”-Ersatz ist die Entscheidung für den rechte Hauptzweig sehr wichtig. Außerdem gibt es hier auch die Option des MicroBlaze als Soft-Prozessor. Wenn Sie diesen Softprozessor nicht haben, führt der Weg zu IGLOO2-Bausteinen mit oder ohne Transceiver, je nachdem, wie es Ihr Design erfordert. Mit einem vorhandenen MicroBlaze können Sie von dem eingebauten ARM® Cortex M3 Prozessorkerns profitieren, der in den SmartFusion®2-FPGAs vorhanden ist. Als zusätzlichen Vorteil dieses Prozessor-Clusters erhalten Sie auch mehrere integrierte Peripheriebausteine, die Sie bislang traditionell in Ihrer FPGA-Fabric aufbauen mußten. So können Sie einen Baustein mit geringerer Logikkomplexität wählen und damit Ihr System in Bezug auf den Stromverbrauch und alles, was damit zusammenhängt, stark verbessern.

Was sind Beispiele für diese Peripheriebausteine?

– Speicher-Controller für DDR-SDRAM (Double Data Rate Synchronous Dynamic

Random-Access Memory)

– SPI (Serial Peripheral Interface bus) / I²C (Inter-Integrated Circuit bus interface) /

UART (Universal Asynchronous Receiver Transmitter) / Timer (jeweils zwei)

– CAN (Controller Area Network bus)

– WDT (Watch-Dog-Timer)

– Ethernet

– DMA (Direct Memory Access)

Zusätzlich verfügen die SmartFusion®2- und IGLOO2®-Bausteine über einen eingebetteten nichtflüchtigen Speicher (eNVM) von bis zu 512kB, abhängig von der Bausteingröße.

Basierend auf diesem Entscheidungsbaum haben Sie einen Eindruck davon, welche Gerätefamilie Sie verwenden sollten. Der nächste Schritt ist die Beurteilung des Aufwands für eine Portierung auf diese Familie. Da sich die meisten meiner Gespräche in letzter Zeit um einen unmittelbaren Bedarf drehten, werde ich zeigen, wie einige Konvertierungsschritte aussehen, um einen SmartFusion®2-SoC oder IGLOO2®-FPGA zu verwenden.

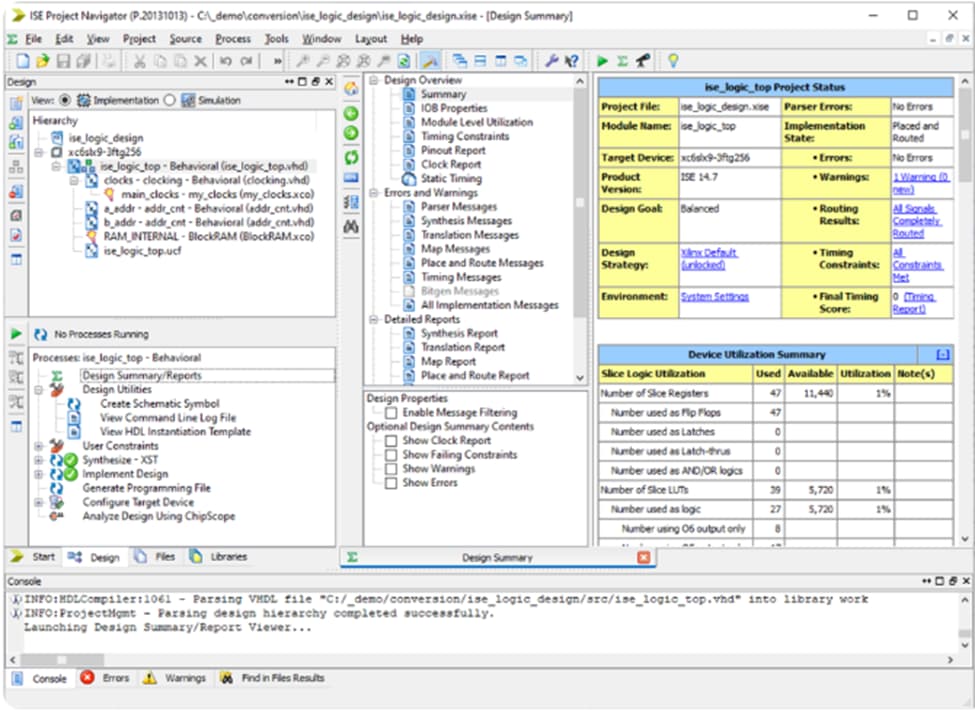

Entwurfsmigration von ISE zum Libero® SoC Tool

Eine unzweifelhafte Voraussetzung für die Migration von Spartan®-6 auf irgendetwas Anderes, einschließlich Spartan®-7, ist die Tool-Migration. Spartan®-6 beruht noch auf Xilinx‘ ISE® Design Suite, Spartan®-7 benötigt Vivado® und Microchip‘s FPGAs benutzen deren Libero® SoC (System on Chip).

Für Spartan-6 wurde in der Regel eine kostenlose ISE WebPack® Version verwendet.

Für Libero Software ist die entsprechende kostenlose Version eine Silberlizenz zu Libero® SoC, die hier heruntergeladen werden kann:

Die kostenfreie Lizenz kann hier angefordert werden:

Die gute Nachricht aber ist, daß Libero® SoC sich nicht allzu sehr von der Xilinx‘ ISE® Software-Umgebung unterscheidet, Sie werden sich leicht zurechtfinden:

Die beiden Bilder oben zeigen dasselbe Design, das in ISE und Libero SoC geladen wurde. Beide Tools verfügen über Projektmanagementfunktionen für die Implementierung und Simulation. Die Screenshots zeigen die Hierarchie des Designs und ermöglichen die Navigation im Design. Darüber hinaus ist der Design-Flow auch von diesen GUIs aus zugänglich und führt die Designs von VHDL/Verilog® mit IPs und Constraints zum Bitstream für das FPGA zusammen.

Da Spartan-6-Anwender mit Libero SoC als Werkzeug wahrscheinlich noch nicht ganz so vertraut sind, haben mein Kollege Miguel Idiago Valero und ich ein Python-Skript erstellt, das von einem Werkzeug in das andere konvertiert. Dieses Skript nimmt eine ISE *.xise-Datei und erstellt ein TCL-Skript zum Einrichten eines Projekts mit Ihren Quellen in Libero SoC. Das Konvertierungsskript ist auf Anfrage erhältlich. Die Absicht ist es, bei den ersten Schritten zu helfen, etwas in Betrieb zu nehmen und ein erstes Setup zu haben, jedoch ist dies nicht als vollständige Konvertierung gedacht. Eine bewußte Einschränkung des Konvertierungsskripts ist, daß nur HDL-Quellen übertragen werden. IP-Komponenten haben ein anderes Format und müssen individuell behandelt werden, dasselbe gilt für Constraints.

Wenn Sie das Skript ausführen, werden Sie auch feststellen, daß nicht nur IP-Komponenten fehlen, sondern auch Basiskomponenten wie die Instanziierungen der Unisim®-Bibliothek, sowie der Digital Clock Manager (DCMs) und der globale Clock-Buffer (BUFG) oder Ähnliches.

Für das Clocking ist die erforderliche Nacharbeit ziemlich einfach. Oft kann man einfach die Komponenteninstanzierung von BUFGs durch eine CLKINT-Komponente ersetzen. Um die korrekten Architekturmakros, ihre Instanziierungen und Port-Maps zu erhalten, lesen Sie bitte das Macro Library User Guide:

-

SmartFusion®2 / IGLOO2:

https://www.microsemi.com/document-portal/doc_download/130906-smartfusion2-and-igloo2-macro-library-guide

Um den Digital Clock Manager oder die PLL von Spartan-6 zu verwenden, mußten Sie typischerweise eine IP-Instantiation mit Hilfe einer GUI (Graphical User Interface) erstellen, um die entsprechenden Funktionen in ISE einzustellen:

Für Libero SoC ist der Ansatz ähnlich, man kann eine IP für den Clock Conditioning Circuit aus dem Katalog-Fenster auswählen:

In beiden Fällen wird der Benutzer durch die GUI geführt, um die Design-Anforderungen einzugeben. Daraufhin werden die Basiskomponenten konfiguriert und zeigen die bestmöglichen Übereinstimmungen an. Wenn alle Konfigurationen abgeschlossen sind, werden IP-Komponenten und HDL-Instantiationen für die Instanziierung im Gesamtentwurf erstellt.

Beschränkungen

Libero SoC verwendet SDC-basierte Constraints und erlaubt sowohl einen text- als auch einen GUI-basierten Ansatz zur Erstellung dieser Constraints. Das Bild unten zeigt die GUI des Constraints-Editors, der zur Erstellung der SDC-Befehle für die Eingabe der Clock-Constraints, aber auch für falsche Pfade oder Multicycle-Constraints verwendet wird.

Mit diesem GUI können Sie Ihre Design-Komponenten filtern, um die entsprechenden Clock- oder Enable-Quellen auszuwählen und damit das Timing einzustellen.

Für IO-Constraints gibt es ähnliche GUIs, die eine Drag- und Drop-Zuweisung einzelner Ports oder ganzer Schnittstellen wie bei DDR-Speichern erlauben. Dies macht die Verwendung von Microchip FPGAs als Ersatz insgesamt sehr einfach.

Für diejenigen unter den Lesern, die einen skriptbasierten Ansatz für ihr Design bevorzugen, ist der Design-Flow in Libero SoC vollständig skriptbar.

Eingebettete Verarbeitung

Der übliche eingebettete Prozessor in Spartan-6 ist der MicroBlaze-Softprozessor, der mit FPGA-Fabric implementiert wird und oft mit Taktfrequenzen zwischen 66 MHz und 100 MHz läuft. Da die SmartFusion®2-SoCs bereits ein Mikrocontroller-Sub-System (MSS) enthalten, ist der vorgeschlagene Weg zur Konvertierung eines MicroBlaze, die Verwendung dieses MSS mit seinem ARM Cortex M3.

Um von MicroBlaze auf M3 zu portieren, ist eine manuelle Einrichtung des MSS erforderlich. Dabei hilft die Bus-Interface-Ansicht des Xilinx Platform Studio:

In dieser Ansicht kann man die verschiedenen Komponenten und deren Verbindung sehen. In Libero SoC muß man nur den MSS mit seiner vorhandenen Peripherie über einen SmartDesign-Block konfigurieren:

Die verfügbaren Peripherie-Interfaces sind Teil des in Hardware implementierten MSS und daher ist kein Adress-Setup erforderlich. Die Auswahl bzw. Abwahl einer bestimmten Peripherie erfolgt über die kleine Tick-Box am unteren rechten Rand jedes Funktionsblocks. Neben dieser Klick-Box befindet sich ein zusätzliches Icon, mit dem man die Eigenschaften der IPs einstellen kann und ob sie über die dedizierten MSS-IOs oder über die FPGA-Fabric aus dem Gerät geroutet werden sollen.

Dieser SmartDesign-Block mit seiner MSS-Konfiguration kann entweder in einem blockbasierten SmartDesign verwendet oder in ein HDL-Design instanziiert werden. Abhängig von Ihrem ursprünglichen Design können Sie die eine oder die andere Option bevorzugen.

Wichtige Unterschiede

Der Hauptunterschied zwischen einem Spartan-6 und einem Microchip-FPGA besteht in der Handhabung des Bitstroms. Microchip-FPGAs haben die Programmier-Informationen Ihrer aktiven Komponenten direkt in Flash-Zellen gespeichert und benötigen daher nicht bei jedem Einschalten (Power-Cycle) eine Konfiguration. Dadurch kann ein externer SPI-Flash-Speicher überflüssig werden.

Mit den Vorteilen des Flash-Prozesses werden jedoch auch einige Nebeneffekte eingeführt, die das Design beeinflussen können:

– Flipflops in Microchip FPGAs benötigen beim Einschalten einen Reset, um einen definierten Zustand zu erreichen. Potenzielle INIT-Werte, die auf Signaldeklarationen im HDL basieren, können nicht für die Implementierung verwendet werden und das Synthese-Tool gibt eine entsprechende Warnung aus. Von Designs ohne Reset wird abgeraten.

– LSRAMs in SmartFusion®2 und IGLOO2 können beim Einschalten nicht initialisiert werden, sondern müssen geladen werden, wenn sie als ROM verwendet werden sollen. AC392 (https://www.microsemi.com/document-portal/doc_download/129978-ac392-smartfusion2-soc-fpga-sram-initialization-from-envm-libero-soc-v11-7-application-note) enthält Beispiele, wie dies unter Verwendung des eNVM als Speicher für Initialisierungsdaten erreicht werden kann und wie die LSRAMs entweder über die M3 oder die Fabric-Logik geladen werden können.

– Die Ein-/Ausgänge (I/Os) des Spartan-6 können alle mit 3,3 V betrieben werden, während SmartFusion®2 und IGLOO2 eine Kombination von I/Os im Bereich von 3,3 V und 2,5 V für höhere Leistung bei geringerem Stromverbrauch bieten. Wenn Sie viele 3,3-V-IOs verwenden, müssen Sie möglicherweise einige zusätzliche Überlegungen zu Ihrem neuen Gehäuse anstellen. Diese Tabelle gibt einen Überblick über die Anzahl der 3,3V- und 2,5V-IOs in den verschiedenen Geräte- und Gehäusekombinationen:

| FCS325 | VF256 | VF400 | TQ44 | FG484 | FG676 | FG896 | |

|---|---|---|---|---|---|---|---|

| Größe | |||||||

| (mm) | 11x11 | 14x14 | 17x17 | 20x20 | 23x23 | 27x27 | 31x31 |

| M2*005 | 119/42 | 79/72 | 52/32 | 115/94 | |||

| M2*010 | 66/72 | 99/96 | 52/34 | 123/110 | |||

| M2*025 | 94/86 | 66/72 | 111/96 | 157/110 | |||

| M2*050 | 94/86 | 105/162 | 139/238 | ||||

| M2*060 | 114/88 | 111/96 | 157/110 | 271/116 | |||

| M2*090 | 104/76 | 157/110 | 309/116 |

Die Unterstützung von 3,3 V an 2,5-Volt-Eingängen für IGLOO2/SmartFusion®2 kann auf folgende Weise erreicht werden, die im User Guide UG0445 dokumentiert ist:

UG0445 gibt in Kapitel 6.12 Vorschläge zu Widerständen und deren Einfluß auf die damit nutzbare maximale Datenrate.

Die Widerstände wirken sowohl als Spannungsteiler als auch als Strombegrenzer in den IO.

Kein vorzeitiges Ende der Lebensdauer

Microchip hat eine etablierte und bewährte No-End-of-Life-Praxis, deren FPGAs werden nicht abgekündigt! Somit können Sie getrost in die Zukunft blicken, denn die Verfügbarkeit von SmartFusion®2- und IGLOO2-Bausteinen wird für mindestens für die nächsten 15 Jahre ab heute und sogar für mindestens 20 Jahre für die PolarFire Serie kommuniziert und unterstützt. Diese kühne Behauptung wird durch die Geschichte bewiesen: Bauteile, die Ende des letzten Jahrtausends eingeführt wurden, sind heute immer noch erhältlich.

Wenn Sie sich für FPGAs von Microchip entscheiden, können Sie sich auf eine lange Lebensdauer verlassen und brauchen sich keine Sorgen mehr über erneuten Entwicklungsaufwand Ihrer Geräte wegen Bausteinabkündigung machen.

Zusammenfassung

Der Umstieg von Xilinx Spartan-6 auf Microchip FPGAs, insbesondere SmartFusion®2 und IGLOO2, ist recht einfach und mit vertretbarem Aufwand möglich zu realisieren. Falls Konvertierungsunterstützung erforderlich ist, sind mehrere Stufen möglich, von der schlüsselfertigen Konvertierung durch Microchip Design Services oder Design Partner bis hin zu einfachen technischen Gesprächen über die Wahl des richtigen Bausteins.

Beginnen Sie Ihre Zukunft noch heute mit uns !

Im Original zuerst Veröffentlicht von

Martin Kellermann Author und Marketing Business Development Manager at Microchip Technology Inc.

Ich habe versucht, eine einfache Möglichkeit zu finden, das Konvertierungsskript interessierten Nutzern zur Verfügung zu stellen und habe mich entschieden, Microsoft Forms dafür zu verwenden.

Wenn Sie daran interessiert sind, das Konvertierungsskript zu erhalten, füllen Sie bitte dieses Formular aus:

Protect your Future with a Microchip FPGA device in place of Spartan®-6 | LinkedIn