세라믹 커패시터

세라믹 커패시터는 일반적으로 티탄산 바륨(BaTiO3)에 기반한 다양한 세라믹 유전체 사용을 특징으로 하는 정전기 소자입니다. 또한 대부분의 수량-품질 스펙트럼(품질에 약간 편향될 수 있음)을 포괄하는 특성을 가진 무극 소자입니다. 구조와 유전체 속성을 다양하게 변형하여 다양한 응용 분야의 요구 사항을 충족할 수 있습니다. 이러한 폭넓은 적용 가능성과 상대적으로 낮은 비용 구조로 인해 세라믹 커패시터는 판매된 소자 수를 기준으로 현재 가장 널리 사용되는 커패시터 유형입니다.

소자 구조

초기 소자는 두 금속 전극 사이에 세라믹 유전체 단일 층(일반적으로 원형)이 있는 구조였습니다. 금속 전극에 리드를 부착하고 이 조립품을 절연 소재(일반적으로 세라믹 또는 에폭시)로 봉합하였습니다. 이 구조 유형은 AC 라인 또는 고전압 응용 분야 용도의 소자에서 여전히 발견되지만, 이 구조 방식에 기반하는 소자가 표면 실장에 적합한 경우는 거의 없어서 많은 응용 분야에서 관심을 끌지는 못합니다.

전체 체적이 작은 패키지에서 큰 전극 표면적을 실현하기 위해, 오늘날에는 얇은 전극 층과 유전체 층이 교차하여 끼워져 있는 적층 세라믹 칩 커패시터(MLCC)가 일반적으로 사용됩니다. 이러한 소자는 미세 분말 형태의 전극 소재가 스크린 인쇄와 유사한 공정을 통해 증착된 얇은 무소성 세라믹 “클레이” 시트들을 압출하여 만듭니다. 다수의 이 "시트"들을 적층 및 압축하여 원하는 수의 전극층을 만들고, 개별 커패시터로 자른 후, 세라믹 유전체를 경화하고 분말이 금속 전극에 융합될 수 있도록 고온의 오븐에서 소성합니다. 그런 다음 외부 전극을 적용하고, 최종 검사를 통과한 소자는 배송을 위해 포장됩니다.

위: 간소화된 MLCC 생산 공정(출처: WikiMedia Commons)

사용 가능한 정전 용량과 전압 범위:

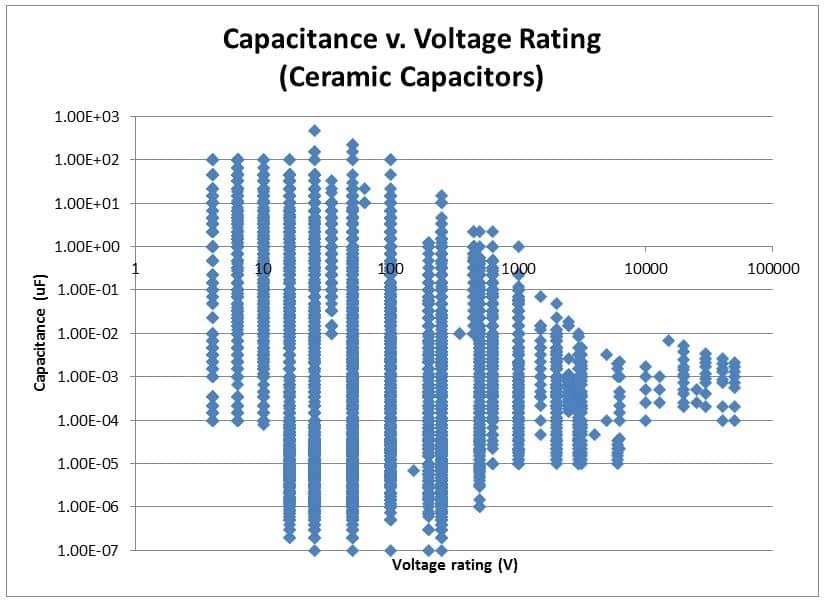

아래 차트는 이 기사를 작성하는 시점에 Digi-Key에서 구입가능한 세라믹 커패시터의 전압/정전 용량 조합 범위를 보여줍니다. 차트는 두 축 모두 로그입니다.

응용 분야의 장단점

세라믹 커패시터(특히 MLCC)는 다용성, 경제성, 내구성 및 일반적으로 우수한 전기적 특성으로 인해 많은 사랑을 받고 있습니다. 응용 분야가 겹치는 경우, 세라믹 커패시터는 대량 전력 처리에 사용되는 다른 유형(예: 알루미늄, 탄탈룸)에 비해 우수한 특성을 가지며, 최상의 안정성 또는 정밀도가 요구되는 곳에 사용되는 박막 또는 다른 유형에 비해서는 다소 열등한 특성을 가집니다.

세라믹 커패시터의 다용성은 위의 차트에 설명된 대로 정전 용량은 약 아홉 자릿수, 전압은 네 자릿수의 사용 가능한 값의 범위가 반영된 것입니다. 이 정도 범위를 포괄하는 기술은 많지 않습니다. 대부분의 경우 세라믹 커패시터 구조에 사용되는 원자재는 특별히 비싸지도 않고 효과적으로 활용되며, 높은 수준의 정밀도와 공정 제어가 요구되지만 기본 제조 공정은 크게 복잡하지 않습니다. 이러한 특성으로 인해 1센트도 되지 않는 단위 비용으로 매년 수십억 개의 MLCC를 생산할 수 있습니다. 응용 분야의 측면에서 세라믹 커패시터는 장기간 사용할 수 있는 응용 분야에 적합합니다. 기본적으로 내구성이 뛰어난 소재(금속 및 세라믹)가 층층히 쌓인 케이크와 같아서 마모 메커니즘이 강력하지 않고, 온도, 압력 또는 역전압에 크게 취약하지 않으며, 전해 소자에서 다양하게 발생하는 누출, 연소 또는 독성의 위험이 없습니다. 세라믹 커패시터의 동작은 전해 소자처럼 상대적으로 고저항인 전해질 용액에 의해 결정되지 않기 때문에 세라믹 커패시터의 ESR은 매우 낮은 경향이 있으며, (MLCC의 경우) 내부 구조와 짧은 리드 길이로 인해 대부분의 경우 기판 레이아웃이 ESR에 가장 크게 기여합니다.

세라믹 커패시터 응용 분야의 단점에는 세라믹 유전체의 특정 물질에 따른 기계적 취약성, 자기 회복 기능 부재, 높은 정전 용량에서의 비용, 환경 및 전기적 동작 조건에 따른 다양한 수준의 파라미터 종속성 등이 있습니다.

대부분의 세라믹 물체와 마찬가지로 세라믹 커패시터도 깨지기 쉽고 유연성이 떨어집니다. 그 결과, 기계적 스트레스나 열 충격에 의한 손상에 취약하므로 최종 제품의 조립 및 운영 시 이러한 요소들을 신경 써서 완화시켜야 합니다. 상대적으로 비활성인 세라믹 커패시터의 "강철과 돌"이라는 구조의 단점은 자기 회복 매커니즘이 없다는 것입니다. 절연 파괴를 초래하는 스트레스는 소자에 회복할 수 없는 손상을 초래하는 경향이 있으며, 생산 중에 유전체의 취약점을 쉽게 "제거"할 수 없으므로 실질적으로 안전 요인을 강화하려면 유전체 두께를 증가시키는 수 밖에 없습니다. 따라서 전해 소자에 비해 세라믹 커패시터의 패럿당 비용은 상대적으로 높아지고 소자의 크기가 커질수록 기계적 손상 위험도 증가하여, 수십 uF 이상 세라믹 커패시터는 매력 및 가용성이 감소하는 결과를 초래합니다. 마지막으로, 대부분의 세라믹 유전체 조성은 일반적으로 유전 상수에 비례하는 정도까지 온도 및 유전 응력에 대해 파리미터적으로 안정적이거나 선형적이지 않습니다. 그 결과, 정전 용량이 높은 세라믹 커패시터는 대체로 정밀 응용 분야에 적합하지 않습니다.

중요한 설계 고려 사항

온도 특성 및 유전체 분류

다양한 세라믹 유전체가 일반적으로 사용되고 있으며 체적 효율, 온도 종속성, 손실 특성 및 기타 비이상적인 동작이 각기 다릅니다. 다양한 소자가 온도 특성에 따라 분류되며 EIA(Electronics Industry Association, 전자 산업 협회), IEC(International Electrotechnical Commission, 국제 전기기술 위원회)뿐만 아니라 미군 및 기타 표준 기구에 의해 수년 동안 다양한 경계선과 식별 시스템이 마련되어 있습니다.

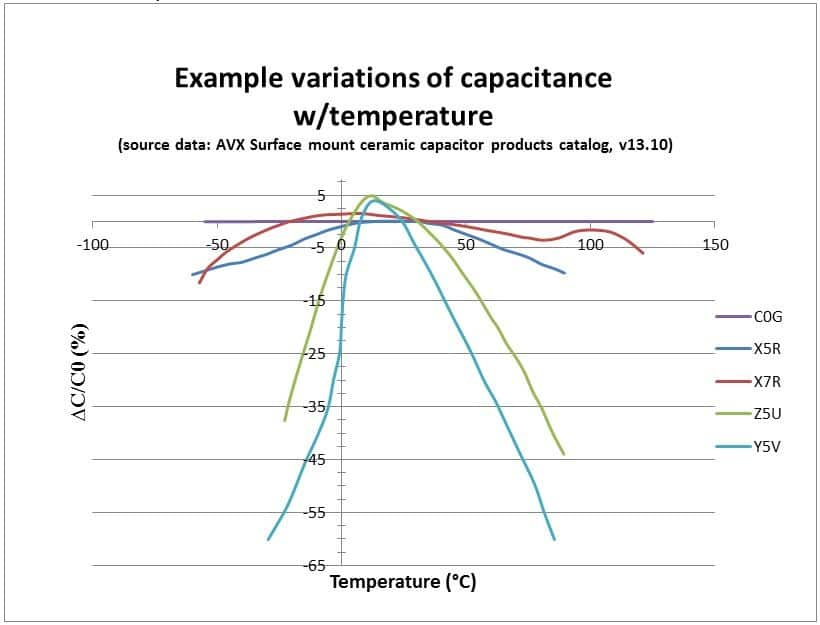

이러한 시스템간의 공통점은 정전 용량의 품질과 수량의 차이에 있습니다. 정밀 아날로그 및 공진 회로 응용 분야에 사용되는 저손실/고안정성/온도 선형적 유형은 안정성과 선형성을 희생하여 체적당 높은 정전 용량을 제공하는 유형과는 다르게 취급됩니다. IEC 표준에서는 정전 용량의 품질과 수량을 위해 설계된 유전체를 각각 클래스 1 및 클래스 2로 지정합니다. IEC 표준과 마찬가지로, EIA 표준에서는 품질 중심 유전체를 클래스 I(로마 숫자, 항상 사용되지는 않음)로 지정하고, IEC 클래스 2 소자를 EIA 클래스 II 및 III으로 세분화합니다. EIA 클래스 II 소자는 온도에 대한 파라미터 안정성에 관하여 어느 정도 체면(일반적으로 -50°C ~ 85°C 이상의 규정된 범위에 대해 +/- 15% 이상)을 유지하는 소자인 반면, EIA 클래스 III 유전체는 체적 효율을 추구하여 온도 안정성을 구실로 삼는 모든 것을 포기해서 좁은 온도 범위에 비해 파라미터 변화가 큽니다. +10°C ~ +85°C에서 +22%/-56% 또는 -30°C ~ +85°C에서 +22%/-82%가 일반적인 클래스 III 허용치입니다. 아래 차트는 이 현상을 그래픽으로 나타내 한 제조업체의 몇 가지 다른 온도 특성을 가진 유전체 특성을 보여줍니다.

다양한 유전체 조성을 각 일반 유전체 클래스에서 사용할 수 있으며, 클래스 1 유전체의 경우 정전 용량의 온도 계수에 의해, 그리고 다른 소자 클래스의 경우 지정된 온도 범위에서 정전 용량 변화에 대한 제한에 의해 분류됩니다.

일부 분류 체계에 대한 "암호 해독 링(Secret decoder ring)"이 아래 표에 나와 있습니다. IEC 클래스 1(EIA 클래스 I) 유전체로 만들어진 MLCC는 통제되고 지정된 정전 용량 온도 계수에 따라 설계됩니다. 이 소자의 정전 용량은 온도에 선형인 함수입니다. EIA 클래스 I 소자의 유전체 분류는 이 선의 기울기와 해당 기울기의 허용 오차를 모두 나타냅니다. 대조적으로, 클래스 II 및 III 세라믹의 유전체 분류는 1) 온도에 따른 정전 용량의 변화, 즉 표준 온도(일반적으로 25°C)에서의 값에 대한 백분율 및 2) 경계가 적용되는 온도 범위라는 두 가지 크기에 대한 최대 경계를 나타냅니다. 이러한 한계치 내에서의 온도 특성 기울기에 대해서는 어떠한 암시도 없습니다. 대부분의 경우 변화가 많고 훨씬 덜 선형적입니다.

IEC 클래스 2(EIA 클래스 II/III) 유전체의 분류와 관련하여 중요한 두 가지 관찰이 이루어져야 합니다.

-

이 분류는 온도에 따른 정전 용량 변화만 나타냅니다. 다른 영향은 ΔC 수치에 포함되지 않으며 이러한 영향이 상당할 수 있습니다. (정전 용량의 전압 계수 부분 참조)

-

이 분류가 유전체 조성에 대한 절대적인 규정은 아니며, 온도 동작에만 기반하여 소자를 그룹화하는 수단일 뿐입니다. 부품 번호가 다르면(특히 패키지 크기가 다른 부품이면) 값, 허용 오차, 전압 정격, 유전체 분류가 같더라도 주어진 응용 분야에서 다르게 동작할 수 있습니다.

허용 오차 사양

세라믹 커패시터의 제조 허용 오차와 온도 동작 사양간의 구분은 자리 수 크기의 유사성, 둘 다 백분율로 표현하는 일반적인 관행 및 불완전한 언어학적 규칙으로 인해 오해 받기 쉽습니다. 정확히 말하면, 세라믹 커패시터에서 “허용 오차” 사양은 제조 변동성으로 인해 표준 테스트 조건에서 허용되는 소자 값 차이를 나타냅니다. 이 사양은 일반적으로 공칭 값의 백분율로 지정되며, 공칭 값을 기준으로 표준화된 테스트 조건에서 동일한 부품 번호인 다른 소자 간의 차이를 나타냅니다. 달리 말해, 제조 라인에서 나오는 부품의 균등성 척도입니다.

반면에, 세라믹 커패시터의 "온도 특성"은 주어진 소자의 정전 용량이 해당 소자의 명시된 동작 온도 범위에서 온도에 따라 변경될 것으로 예상되는 정도를 나타냅니다. "온도 계수"라는 용어는 다소 선형적인 온도 종속성을 갖는 클래스 I 유전체를 사용하는 소자에 가장 적합한 반면, "온도 특성"이라는 용어는 온도에 따른 정전 용량 변화가 확실하게 비선형적인 EIA 클래스 II 및 III 유전체를 사용하는 커패시터에 더 적합합니다.

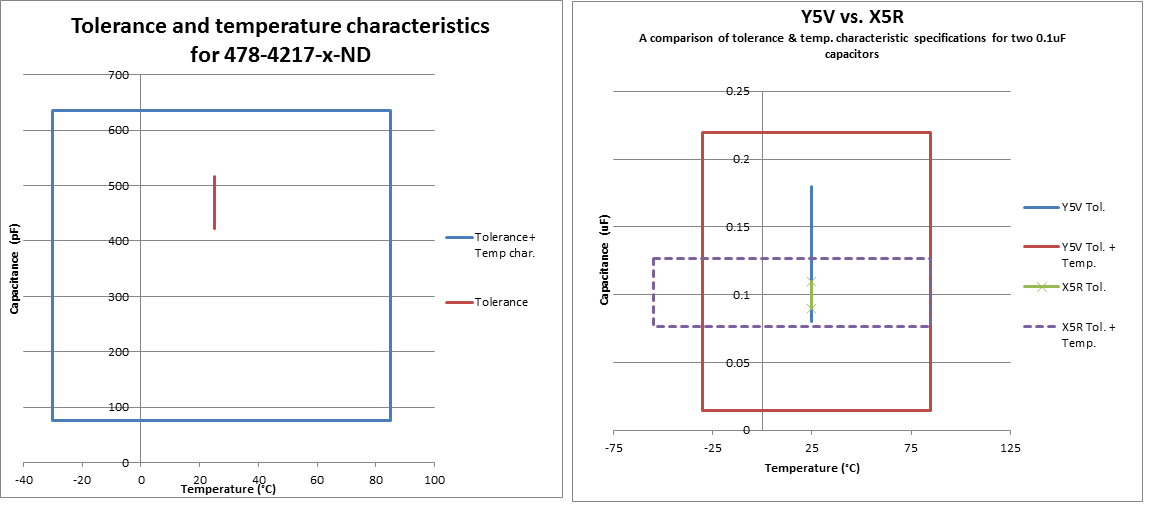

예를 들어, 부품 번호 478-4217-1-ND는 470pF의 공칭 정전 용량, +/-10%의 허용 오차 그리고 Y5V의 온도 특성을 갖는 것으로 명시된 세라믹 디스크 커패시터입니다. 지정된 테스트 조건에서 측정할 때 이 부품 번호로 된 소자는 423pF ~ 517pF 사이의 정전 용량을 나타낼 것입니다. 이는 소자의 허용 오차이며 아래 왼쪽 그래프의 빨간색 선 위 어떤 지점이 이 부품 번호로 된 소자를 설명할 것입니다. 그러나 Y5V 온도 특성은 표준 테스트 조건에서의 정전 용량 값에 비해 -30°C ~ +85°C 사이의 온도에서 측정할 때 소자의 정전 용량이 추가로 +22%/-82% 변경될 수 있다는 것을 의미합니다. 다시 말해, 지정된 테스트 신호, 지정된 온도 기록 등으로 측정된 정전 용량 대 온도 그래프가 파란색 박스를 세로로 벗어나지 않고 빨간색 선을 통과하는 한 소자는 사양을 충족합니다. 박스의 가로(온도) 한계는 벗어나더라도 상관이 없습니다. 온도 특성을 고려할 때, 이 (공칭) 470pF 커패시터는 사양을 완전히 충족하면서도 76pF ~ 630pF(25°C에서는 제외) 사이의 정전 용량을 나타낼 수 있습니다. 노화와 전압 효과를 변수로 추가할 경우 실제로 관찰되는 정전 용량은 소자의 지정된 한계를 넘지 않은 채 훨씬 더 넓은 범위로 달라질 수 있습니다. 여기서 "허용 오차"와 "온도 특성"의 구분이 매우 중요합니다. 소자가 공칭값의 10% 이내일 것으로 오해하는 설계자는 응용 제품이 상온에서 많이 벗어날 경우 실망할 가능성이 높습니다.

동일한 EIA 0402 패키지에 0.1uF, 25v 커패시터인 부품 번호 490-3271-2-ND와 490-5920-2-ND를 비교해보겠습니다. 전자는 Y5V 특성을 가진 클래스 III 유전체를 사용하며 허용 오차는 -20%~+80%, 그리고 이 기사를 작성하는 시점에 대량 구매시 단가는 $0.00399입니다. 후자는 X5R 특성을 가진 클래스 II 유전체를 사용하며 허용 오차는 +/-10%, 그리고 $0.00483에 판매됩니다. 온도 특성을 고려한 허용 오차 대역과 영역이 위 오른쪽 차트에 함께 표시되어 있습니다. 왼쪽 차트와 마찬가지로 조립 라인에서 나온 소자의 온도에 따른 실제 정전 용량이 각자의 박스를 벗어나지 않고 25°C의 세로선을 통과한다면 이들은 사양을 충족하는 것입니다. X5R (클래스 II) 소자는 Y5V (클래스 III) 소자보다 더 넓은 온도 범위에서 공칭 값에 3배 이상 더 가깝게 유지되는 반면, 제조 변동성과 온도가 결합된 효과로 인한 최대 소자 값과 최소 소자 값의 비율은 클래스 II 소자의 경우 거의 10배 더 낮습니다. 1/10센트도 되지 않는 비용으로 필요한 설계 마진 감소, 생산 수율 향상, 테스트 요구 사항 감소, 제품 수명 향상 등을 실현할 수 있습니다. 이러한 혜택은 그 만한 가치가 있지만 그렇게 많은 비용이 들지 않습니다.

정전 용량의 전압 계수

세라믹 커패시터는 DC 전압 레벨의 변화에 따라 정전 용량이 변경됩니다. 달리 말하면, 평균 0V인 1V p-p 사인파로 소자의 정전 용량을 측정하면 동일한 소자를 DC 오프셋이 10V인 1V 사인파로 측정할 때와 다른(일반적으로 더 큰) 값이 나올 것입니다. 이 효과는 인가 전압이 변화함에 따라 유전체의 결정 구조에 가해지는 스트레스에 기인하며, 결과적으로 유전체 두께/소자 전압 정격에 따라 증가합니다. 좀처럼 그렇지 않지만 다른 조건이 모두 같다면, 100VDC 정격인 소자가 동일한 비율의 정전 용량 변화를 나타내기 위해서는 25VDC 정격인 소자보다 4배 더 큰 DC 바이어스가 필요합니다. 당연하게도 이 효과는 유전체 조성의 영향을 받습니다. EIA 클래스 I 유전체의 전압 계수는 상대적으로 작으며, 소자 정격 전압의 0% ~ 100% 사이에서의 DC 전압 변화에 따른 관찰되는 정전 용량 변화는 일반적으로 기껏해야 몇 퍼센트(보통은 더 작음) 입니다. EIA 클래스 II 유전체는 DC 전압의 영향을 훨씬 크게 받으며, 약 20% ~ 60%의 정전 용량 변화가 일반적입니다. 이러한 변화가 가볍게 볼 정도는 아니지만 정격 전압에서 일반적으로 80% ~ 90% 이상의 정전 용량 변화를 나타내는 EIA 클래스 III 유전체에 비하면 훨씬 양호합니다. 아니요, 오타가 아닙니다. EIA 클래스 III 유전체를 사용하는 세라믹 커패시터의 유효 정전 용량은 단순히 DC 전압에 따라 크게 변화할 수 있습니다. 이 효과 또한 불친절하게도 비선형적일 수 있습니다. 일부 소자는 정격 DC 전압의 20%만 인가되어도 정전 용량의 75%가 감소할 수 있습니다. 설상가상으로, 이 효과는 온도 효과와 함께 비선형적으로 누적됩니다.

DC 전압 효과의 크기와 소자 패키지 크기 사이의 관계는 더욱 놀랍고 점진적입니다. 더 작은 패키지에 더 큰 정전 용량을 주입하는 것은 어느 시점에 타협이 필요하며, 동일한 제조업체의 제품 계열인 세 가지 서로 다른 1uF/16V/X5R 커패시터의 DC 전압에 따른 정전 용량 변화를 보여주는 위 차트에서 해당 시점을 설명합니다. 여기서 세 커패시터의 주요 차이점은 패키지 크기뿐입니다. 작아지는 패키지의 반대급부는 명확합니다. EIA0805 패키지 소자(녹색)는 5V 전압에서 정전 용량 손실이 수 퍼센트이지만, 보다 공격적인 0402 패키지 소자(파란색)는 동일한 조건에서 손실이 약 70%이며, 0603 패키지 소자(빨간색)는 그 사이 어딘가입니다(데이터 출처: TDK Components Characteristic Viewer 온라인 도구). 대부분의 응용 분야가 DC 전압과 일부 최소 정전 용량을 유지(예: 저손실 전압 조정기의 출력 필터)하는 것에 대한 관심을 포함한다는 것을 상기한다면 무지의 가능성은 분명히 반갑지 않은 패널티를 초래합니다. 안타깝게도, 이러한 전압 의존 효과는 실질적으로 소자 규격서에 설명되어 있지 않기 때문에, 이들의 존재를 간과하거나 모르는 상태로 지내기 쉬우며 다른 제품을 비교하려면 복잡한 노력이 필요합니다. 하지만 소자를 선택할 때 이러한 효과가 존재한다는 사실을 명심해야 합니다.

균열

세라믹 소재의 깨지기 쉽고 상대적으로 유연하지 않은 특성으로 인해 기계적 손상은 세라믹 커패시터 고장의 주된 원인입니다. 전기적 고장 증상은 주로 정전 용량 감소, 단락 또는 개방 회로로 나타날 수 있습니다. 경우에 따라 온도와 같은 외부 영향으로 인해 이러한 증상이 나타났다 사라졌다 하는 것처럼 보일 수도 있습니다. 세라믹 커패시터의 균열이 육안으로 보이는 경우도 있고, 너무 작아서 보이지 않거나, 실장된 소자의 밑면이나 단자 가장자리에 숨겨져 있는 경우도 있습니다. 기계적 손상은 일반적으로 다양한 메커니즘 중 하나를 통해 발생합니다.

- 조립 중 또는 거친 취급이나 커넥터를 억지로 결합하는 힘에 의한 기판 휨

- 동작 온도 반복 또는 조립 작업에서의 열로 인한 스트레스

- 조립 전 또는 조립 도중 잘못된 취급으로 인한 직접적인 손상

단연코, 적층 세라믹 칩 커패시터(MLCC) 유형은 세라믹 소재, 전극 그리고 PCB 간의 단단한 기계적 결합으로 인해 균열 피해를 가장 많이 입었습니다. 스루홀 또는 리드 프레임 실장 소자의 상대적으로 길고 유연한 전극은 세라믹 커패시터 본체에 가해지는 온도 반복 또는 기판 휨에 의한 힘을 감소시켜 이러한 소자에서 균열이 발생할 가능성을 크게 낮춥니다. 가혹한 사용 조건이 적용되는 응용 분야의 경우, 전극과 세라믹 소자 본체 사이의 기계적 유연성이 향상된 MLCC와 단락 고장의 위험을 완화하도록 설계된 소자를 사용할 수 있습니다. 커패시터 균열의 원인 중 대부분은 조립과 관련이 있으며 설계자가 직접 제어할 수 없습니다. 예를 들어 픽앤플레이스 작업 중에 부품이 부서지거나 파괴되는 것을 방지하고 사용되는 조립 공정에 적절한 예열 및 냉각 시간을 제공할 책임은 조립자에게 있습니다. 사용된 솔더 페이스트의 양/페이스트 스텐실 두께와 같은 요소는 공동의 책임이지만, 패드 크기, 기판 레이아웃, 패키지 선택과 같은 요소는 전적으로 설계자의 책임입니다.

MLCC 균열 현상 및 예방 방법에 관한 자세한 내용은 Cracks: The Hidden Defect(John Maxwell)와 같은 산업 문헌에서 확인할 수 있으며, 여기서는 간소화를 위해 반복하지 않겠습니다. 그러나 어렵사리 얻은 이 지식에서 추출한 다음과 같은 설계자를 위한 몇 가지 중요한 규칙이 있습니다.

- 경험이 풍부하고 품질을 중시하는 조립 업체와 계약합니다.

- 열 충격을 방지합니다. 웨이브 납땜 및 전통적인 납땜 인두는 MLCC에 특히 위험한 조립 및 재작업 방법입니다.

- 부품 크기를 줄입니다. 소자가 클수록 기판 휨에 따른 스트레스가 더 크며, 열 충격에 의한 손상에 더 취약합니다. 0805(2012 미터법) 이하 패키지 소자를 사용하는 것이 좋습니다.

- 조립 후 패널화된 기판들을 절단할 때 기판 휨을 방지할 수 있도록 각별히 주의합니다. v-cut을 따라 어레이를 손으로 직접 분리하는 것이 가장 선호되지 않는 방법이며, 가위를 사용해도 별반 차이가 없습니다. 가능하면 PCB에 휨 스트레스를 주지 않는 톱 또는 다른 분리 방법을 사용합니다.

- 기판 가장자리, 커넥터, 실장 구멍, 크고 무거운 부품, 패널화 탭 또는 PCB에 기계적 스트레스를 가할 가능성이 있는 기타 지점으로부터 MLCC를 멀리 유지합니다. 0.2인치 또는 5mm의 최소 거리를 제안합니다.

노화

세라믹 커패시터는 유전체 결정 구조의 변화와 관련하여 노화 현상이 발생할 수 있으며, 이는 유전체의 초기 소성 이후 정전 용량 및 손실 계수의 변화로 나타납니다. 정석 대로, EIA 클래스 I 유전체는 가장 적은 영향을 받고 노화되지 않은 것으로 간주되는 반면, EIA 클래스 II 유전체는 중간 정도의 영향을 받고, EIA 클래스 III 소재는 매우 큰 영향을 받는 경향이 있습니다. 결정 구조가 다시 형성될 수 있을 정도로 충분히 긴 시간 동안 유전체의 퀴리 온도 이상의 온도에 노출함으로써 이 노화 과정을 재설정(또는 소자 “디에이징”)할 수 있습니다. 이때 온도가 높을수록 필요한 시간이 더 짧습니다. 많은 세라믹 유전체의 퀴리 온도는 대부분의 납땜 공정에서 발생하는 온도보다 낮기 때문에 조립 과정에서 소자가 부분적으로 디에이징될 수 있습니다.

소자의 이 노화 특성은 “마지막 가열” 시 측정된 정전 용량을 기준으로 디케이드 시간당 정전 용량의 백분율 변화로 표현됩니다. 여기서 마지막 가열이란 결정 구조를 완전히 재형성할 정도로 충분히 오래 동안 퀴리 온도 이상으로 가열된 마지막 시간을 의미합니다. 다시 말해, “오븐에서 방금 나온” 상태에서 100uF로 측정된 노화율 (-) 5%인 커패시터는 오븐에서 빼낸 1시간, 10시간 및 100시간 후 각각 95uF, 90uF 및 85uF으로 측정될 것입니다. 소자가 원래 포장에 담긴 상태로 사용되지 않은채 보관되고 있어도 정전 용량이 계속해서 변화한다면 소자의 공칭 정전 용량은 어떤 값이어야 하는지 의문이 제기되는 것은 분명합니다. 산업 표준인 EIA-521과 IEC-384-9에서 이 질문에 대해 다루며, 소자가 마지막 가열 1000시간(약 42일) 후에 지정된 허용 오차값을 충족해야 한다고 명시합니다. 다음 디케이드 시간(10,000시간 및 100,000시간)은 각각 1년 및 11년 이상으로 해석됩니다. 문제를 복잡하게 만드는 것은 노화 과정이 온도에 종속적인 속도로 진행된다는 것입니다. 즉, 유전체의 퀴리 온도까지 소자 온도가 상승하면 일반적으로 노화 과정은 가속화됩니다.

노화 현상으로 인해 소자가 명시된 허용 오차를 벗어난 것처럼 보일 수 있으므로 제품 설계 및 생산 테스트 담당자는 이 사실을 명심해야 합니다. 최근에 리플로우된 조립품을 테스트하면 정전 용량 값은 약간 높을 것으로 예상되며, 소자 노화에도 올바르게 작동할 수 있도록 충분히 여유 있게 설계되어야 합니다. 세라믹 커패시터는 보상 회로 부품 또는 필터 소자로서 전력 변환 회로의 제어 루프에 강력한 영향을 미치므로 전력 변환 회로는 이러한 영향이 중대한 위험을 초래할 수 있는 좋은 예입니다. 조립 중에 디에징된 커패시터의 영향으로 안정적인 것처럼 보이는 시스템이 노화로 인한 정전 용량 손실이 제어 루프의 역학에 영향을 미치면서 시간에 따라 안정성이 저하되는 것을 볼 수 있습니다. 무엇보다 시간에 따른 안정적인 정전 용량 값이 중요한 경우 급격히 노화되는 커패시터는 피해야 합니다. 시지프스가 21세기 인물이었다면 표면 실장 Y5V 세라믹 칩 커패시터를 사용하여 제작된 능동 필터를 조정하는 작업을 했을 것입니다.

압전 효과/마이크로포닉스

IEC 클래스 2(EIA 클래스 II 및 III) 세라믹 유전체는 특성상 압전 효과가 두드러져서 전기적 영역과 기계적 영역 간의 변환 메커니즘이 사소한 수준이 아닙니다. 압전 소재에 전압을 인가하면 기계적 변형이 발생하고, 반대로 압전 소재를 기계적으로 변형하면 압전 소재에 전압이 발생합니다. 커패시터와 PCB 사이의 단단한 기계적 결합으로 인해 표면 실장 MLCC에서 특히 문제가 될 수 있습니다. 한편, 커패시터에 가해진 리플 전압은 성가신 가청 잡음으로 변환될 수 있는 반면에, 외부의 기계적 진동은 전자 회로에 신호로 결합될 수 있습니다. 클래스 1 유전체는 압전 효과가 거의 없기 때문에, 클래스 1 유전체를 기반으로 하는 세라믹 커패시터는 가장 적은 영향을 받습니다. 하지만 모든 커패시터에 내재하는 정전기 효과를 통한 전기 기계적 변환 메커니즘은 여전히 존재하므로, 클래스 I 소자에서는 일반적으로 무시할 수도 있지만 마이크로포닉 효과는 여전히 존재합니다.

전극 금속공학

MLCC의 전극 소재는 귀금속 전극(Noble Metal Electrode, NME) 또는 비금속 전극(Base Metal Electrode, BME) 시스템이라는 두 가지 일반 금속공학 경로 중 하나를 따릅니다. 대부분의 응용 분야에서 일반적으로 선택하는 기준은 아니지만, 두 기술은 특성 차이를 만들므로 유의해야 합니다. 귀금속 전극은 일반적으로 팔라듐-은 합금을 기반으로 하며, 특히 산소에 상대적으로 반응하지 않는 귀금속은 고가이기도 하기에 PME(Precious Metal Electrodes)라고도 합니다. 이러한 전극 소재는 고가라서가 아니라 낮은 반응성 때문에 사용되므로, 비록 이유와 마케팅이 해당 사실에 있어 의견이 다른 것 같지만 NME라는 용어가 더 적절하다고 주장할 수 있습니다. 비금속 전극은 일반적으로 니켈을 기반으로 합니다.

생산 측면에서 당면한 중요한 문제는 세라믹 유전체 소재를 소성하기 위해 필요한 고온에서 전극 금속이 화학적으로 반응하는 방식입니다. 귀금속 전극 시스템은 고온에서 산소가 더 많아도 견딜 수 있으므로, 적절한 경화를 위해 산소가 필요한 대기 분위기 소성로와 유전체 조성을 사용하여 제작할 수 있습니다. 비금속 전극 시스템은 고온에서 산소에 대한 내성이 동일하지 않으므로 다른 장비와 유전체 조성을 사용하여 제조되어야 합니다. NME 접근 방식은 원래 사용된 경로였으며 신뢰성과 업계 경험 축적 측면에서 몇 가지 이점이 있습니다. 따라서 이 기사를 작성하는 시점에 사용 가능한 대부분의 고신뢰성 및 MIL 사양 제품은 이 방법으로 생산되었습니다. 주요 단점으로는 특성 소재와 공정 차이로 인해 NME 소자에서 일반적으로 더 두꺼운 유전층을 사용하므로 BME 소자에 비해 전극 소재의 비용은 높고 체적당 실현 가능한 정전 용량은 낮습니다.

소자 특징, 옵션 및 대상 응용 분야

차량용

“차량용” 유형으로 판매되는 커패시터는 자동차와 같이 기계적으로 까다로운 환경인 응용 분야에 사용하도록 설계되었습니다. 일반적으로 이러한 커패시터는 ESD, 단자에 가해지는 기계적 힘, 서지 전압 등과 같은 다양한 스트레스 메커니즘에 대한 테스트 방법과 성능 수준을 규정하는 자동차 전자 부품 협회에서 제정한 AEC-Q200 표준과 같은 일부 규약에 따라 생산되고 시험됩니다.

ESR 제어형

"ESR 제어"형으로 지정된 커패시터는 정전 용량과 커패시터의 기생 유도 용량에 의해 만들어지는 L-C 회로의 “Q” 계수를 줄이기 위해 소량의 ESR을 의도적으로 추가하여 설계되었습니다. 이는 적정량의 ESR으로 트레이스 인덕턴스에 따른 커패시터의 "링잉"을 줄이거나 병렬 커패시터 간의 반공진 조건 방지에 도움을 줄 수 있는 전원 공급 라인의 디커플링과 같은 응용 분야에 유용합니다.

에폭시 실장형

에폭시 실장형으로 지정된 소자는 일반적인 납땜 공정 대신 전도성 접착제를 사용하여 실장하도록 설계되었습니다. 차이점은 주로 단자의 마감 도금에 사용되는 소재에 있으며, 사용할 실장 방법으로 올바르게 접합될 수 있도록 소재를 달리합니다. 표준 납땜 공정은 에폭시 실장형 소자에 적합하지 않으며 그 반대의 경우도 마찬가지입니다. 납땜 접합부에 비해 향상된 에폭시 접합부의 기계적 유연성은 회로 기판, 납땜 접합부 및 커패시터 본체 사이의 열팽창 계수 차이에 따라 발생하는 기계적 스트레스를 감소시키므로, 에폭시 실장은 온도 변동이 크고 빈번한 자동차 응용 분야와 같은 응용 분야에 유용합니다. 에폭시 실장은 LCD 패널과 같이 열에 민감한 응용 분야에도 유용합니다.

부유 전극

“부유 전극” 유형으로 지정된 소자는 사실상 여러 개의 커패시터가 직렬로 구성되며, 내부 전극이 각 소자 단자에 연결되지 않고 “부유” 상태로 있습니다. 이 구조 방식의 주된 목적은 커패시터 균열의 부차적 영향으로 종종 발생하는 단락 고장 모드의 위험을 줄이는 것이지만, ESD 및 서지 전압에 대한 견고성 측면에서도 유용합니다.

고온

“고온” 유형으로 지정된 소자는 (당연하게도) 대부분의 전자 장비에 가해지는 온도 이상이 가해지는 응용 분야를 위한 것입니다. 이 명칭을 사용하는 소자는 전자 소자에서 일반적으로 볼 수있는 동작 온도 범위의 하한까지 사용할 수 있도록 지정되는 경향이 있으므로 일반적으로 "넓은 온도 범위"를 의미하기도 합니다. 이 명칭에서 명시적으로 알 수는 없지만 대부분의 고온 명칭이 붙은 소자는 온도와 DC 바이어스 모두와 관련하여 해당 종류에서는 다소 인상적인 파라미터 안정성을 보여줍니다.

고전압/Arc Guard™/Arc Shield™

“고전압” 및/또는 특허 받은 아크 방지 명칭이 붙은 커패시터는 전자 소자에 일반적인 응용 전압 이상을 사용할 수 있도록 설계되었습니다. "고전압"이 성립되는 정의는 제조업체마다 다르지만 경계선은 100V ~ 1kV 범위 내에 있습니다. 이러한 전위에서, MLCC 기술은 소자의 외부 막을 통한 단자 사이 또는 단자와 다른 단자에 연결된 전극 사이의 표면 방전에 따른 복잡한 문제에 시달리기 시작합니다. 물론 이는 바람직한 현상이 아닙니다. 표면 방전은 충분히 높은 전압에서 모든 부품에 문제가 되지만, MLCC 기술은 두 개의 소자 단자와 연결된 전극을 매우 근접하게 배치해야 하는 조밀한 구조가 절연 파괴 및 방전 발생 위험을 증가시키기 때문에 특히 취약합니다. 보상을 위해 소자 크기를 증가시키는 것도 한 가지 방법이지만, 그러면 소자 균열 위험이 크게 증가합니다. Arc Guard™ 및 Arc Shield™ 계열 제품과 같은 소자는 이러한 영향을 완화하고, 절연 파괴로 인한 고장 위험과 기계적 균열로 인한 고장 위험 간의 균형 문제를 개선하도록 설계되었습니다.

높은 Q/낮은 손실/낮은 손실 계수

높은 Q, 낮은 손실 또는 낮은 손실 계수 유형으로 판매되는 소자는 ESR을 최소화하도록 설계되었습니다. 일반적으로 이러한 소자는 클래스 I 유전체 소재로 제조되며 주파수 판별 목적으로 거의 이상적인 커패시터가 필요한 RF 또는 기타 고주파 응용 분야에 사용됩니다.

블리드 저항 내장형

이 명칭을 사용하는 소자는 장비에 전원이 공급되지 않을 때 커패시터에 전하가 잔류하거나 발생하지 않을 수 있도록 병렬로 연결된 저항을 내장하고 있습니다. 이 기사를 작성하는 시점에 Digi-Key에는 이 명칭이 붙은 부품 번호가 3개만 등록되어 있으며, 세 부품 모두 재고를 가져가지 않으며 비싼 가격이 책정되어 있습니다. 왜 그럴까요? 이러한 소자 규격서의 첫 페이지인 마케팅 페이지에 기재되어 있는 제안 응용 분야에는 “폭발 장치” 와 "전자 점화"가 포함되어 있으며, 이는 대부분의 커패시터 규격서에서 볼 수 있는 것이 아닙니다. (응용 참고 노트는 제공되지 않습니다…)

낮은 ESL

ESL이 낮은 세라믹 커패시터는 직렬 유도 용량을 최소화할 수 있도록 설계되었습니다. 표면 실장 MLCC의 경우, 이 유도 용량의 대부분은 부품 자체에 내재하는 것이 아니라 패키지의 구조 및 패키지를 회로에 연결하는 리드와 관련이 있습니다. 따라서 ESL이 낮은 MLCC는 대부분 표준 소자에서 구조와 리드 구성이 변형된 것입니다.

다중 단자 낮은 ESL 소자는 각 논리적 커패시터에 대해 여러 개의 물리적 단자를 사용하며 소자를 드나드는 전류에 의해 생성되는 자기장 대부분을 상쇄시키는 방식으로 단자들을 교차시켜 유도 용량을 낮춥니다.

역구조 세라믹 커패시터는 다른 소자에서 흔히 볼 수 있듯이 커패시터의 끝이 아닌 긴 쪽에 소자의 단자를 배치합니다.

스택형 낮은 ESL 세라믹 커패시터는 리드 프레임에 여러 개의 MLCC 소자를 결합하여 하나의 소자인 것처럼 취급 및 조립이 가능하며, 균열과 마이크로포닉 효과 감소의 측면에서 이점이 있습니다. 이러한 소자를 "낮은 ESL"로 설명하는 것은 일종의 마케팅 전략으로, 다른 커패시터 기술과 비교 불가라는 측면에서만 올바르기 때문입니다. 동일한 세라믹 커패시터들을 PCB에 직접 실장하는 것에 비해 리드 프레임에 실장해 기판 위로 쌓아 올려진 소자의 ESL이 훨씬 더 클 것입니다.

낮은 ESL MLCC에 대한 X2Y 설명자는 상표이며, 비슷하게 생긴 "X1Y2"와 같은 안전 지정자와 혼동해서는 안 됩니다. 두 소자 그룹 간에는 사용되는 이유의 측면에서 약간의 먼 유사성이 있지만, 소자 자체는 완전히 다릅니다. 낮은 ESL X2Y 커패시터는 정격 전압이 6.3V에 불과하며 매번 단락 시 고장이 허용되지만, 안전 등급 소자는 kV 수준의 서지를 견뎌야하며 단락 고장 모드를 철저히 방지해야 합니다.

즉, X2Y 낮은 ESR 커패시터는 저전압 전원 공급 디커플링, 공통 모드 필터링 및 유사한 응용 분야에 적용할 경우 매우 유용합니다. 두드러진 특징은 4단자 구조라는 점입니다. 두 단자는 전기적으로 연결되어 있어서 “통과” 연결 및 소자 내 두 개별 커패시터에 대한 공통 단자 역할을 하며, 각 커패시터는 두 번째 전극 연결에 나머지 단자 중 하나를 사용합니다. 이런 기하학적 구조의 배열은 디커플링 응용 분야, 공통 모드 억제 등에서 레이아웃과 관련된 유도 용량을 줄일 수 있습니다.

낮은 높이

높이가 낮은 커패시터는 높이 제약이 심한 응용 분야에서 사용하기 쉽도록 유사한 길이와 너비의 일반적인 소자보다 더 얇게 제조됩니다. 두께가 0.006인치(0.15mm)에 불과한 소자도 사용할 수 있습니다. 이러한 소자의 두께 감소는 소자를 기판 휨에 따른 균열에 더욱 취약하게 만들며, 이러한 소자가 제공하는 추가적인 1~2mm 정도의 높이 감소가 요구되는 응용 분야에서는 더 얇고 (그래서 더 유연한) 회로 기판을 사용할 가능성이 높다는 사실에 비추어 신중한 설계, 조립 및 취급 절차가 두 배로 중요해졌습니다.

군사용

"군사용"이라는 명칭이 붙고 미국 군대의 표준화된 부품 번호 체계에 따라 조달되는 제품은 여러 공급원 간에 제품 일관성을 보장하기 위해 군에서 정한 사양에 따라 생산됩니다.

기존의 “MIL-Spec” 표준에서는 공급업체 간에 균일성과 교체 가능성을 보장하기 위한 노력으로 종류뿐만 아니라 생산 방법도 명시했습니다. 최신의 MIL-PRF 표준은 성능에 기반하며 제품에 요구되는 성능을 지정합니다. 여기서 목표를 달성하는 세부적인 방법은 제조업체의 책임입니다. 후자의 접근 방식에서 제공하는 유연성은 새로운 기술 및 제조 공정을 채택할 수 있는 더 큰 재량을 허용하지만, 시간의 경과에 따라 제조업체 간에 제품 동작에 차이가 발생할 위험이 더 커집니다.

어느 경우든 군사 사양에 따라 조달되는 “실제” 군사용 제품은 광범위한 테스트와 문서화 요구 사항 때문에 다소 많은 비용이 드는 경향이 있습니다. 중간 단계로서 군사 사양에 따라 생산되지만 표준 상용 제품으로 판매되는 제품은 광범위한 문서화 없이 이용할 수 있습니다.

비자기

비자기 커패시터는 자석에 끌리거나 반발하지 않고 놓여진 자기장에 영향을 주지 않는 소재로 제작됩니다. 이 커패시터는 최종 제품이 이러한 특성을 유지하도록 제조 후 선별되기도 합니다. 이러한 제품은 소자가 자기장의 영향을 받거나, 응용 회로 또는 다른 장비의 동작에 영향을 미치는 자기장을 유지하는 것이 바람직하지 않은 의료 영상 및 진단 장비, 내비게이션 시스템, 실험실 장비 및 기타 응용 분야에 사용됩니다.

오픈 모드

“오픈 모드” 소자로 판매되는 MLCC는 기계적 균열로 인해 발생할 수 있는 단락 또는 낮은 임피던스 고장 모드 위험을 줄이도록 설계되었습니다. 이 목적을 달성하기 위해 사용되는 공통된 접근 방식은 두 전극 간에 겹치는 면적을 줄여서 기판 스트레스에 따른 균열의 일반적인 경로가 전극이 겹치는 영역을 통과하지 않도록 하는 것입니다. 이렇게 하면 커패시터 내의 사용 가능한 활성 영역이 감소하고, 그 결과 주어진 패키지 크기에서 실현 가능한 최대 정전 용량 값이 감소합니다.

이 접근 방식을 부유 전극 및 연성 외부 전극 기술과 결합하여 균열이 유발하는 MLCC 고장 관련 위험을 더욱 줄일 수 있습니다. 오픈 모드 MLCC가 단락 고장 위험을 크게 줄이지만 그런 고장의 가능성이 0은 아니라는 사실에 유의하십시오. 단락 고장 가능성을 더 줄여야 하는 경우, 두 소자를 서로 90° 방향이 되게 직렬로 연결해 사용하는 것이 산업 문헌에 제안되어 있습니다.

연성 외부 전극

연성(soft 또는 flexible) 외부 전극으로 판매되는 MLCC는 금속 외부 전극과 세라믹 커패시터 본체 사이에 표준 MLCC에서 볼 수 있는 것보다 기계적 탄력성이 더 뛰어난 결합을 제공하도록 설계되었습니다. 이를 통해 기판 휨 또는 온도 반복으로 인해 세라믹 소재에 가해지는 스트레스의 양을 줄여 균열의 위험을 줄입니다.

영문 원본: Ceramic Capacitors