Vivado Design Suiteを始めたいと思っている方にとっては、このガイドが役に立ちます。Xilinxのプログラマブルロジックデバイスや一般的なプログラマブルロジックデバイスを使い始める簡単な方法を単にお探しかも知れません。 その場合でもこのガイドが役に立ちます。しかし、Xilinxのプログラマブルロジックデバイスと Vivado Design Suiteをスタートプラットフォームとして導入していただく必要があります。このガイドでは、実際のプログラマブルロジックハードウェア、つまり実際の物理的なデバイスで開発を行うことを意図しています。実用的な学習方法であるだけでなく、ご自分のアプリケーションに取り掛かるために必要な基礎知識を得ることができます。

Vivadoと互換性のあるプログラマブルロジックデバイスをベースに構築された開発ボードを使用することができます。現在、Xilinxの7シリーズおよびUltraScaleデバイスを含むすべての新しいデバイスは、Vivadoで動作するように作られています。このガイドの例では、プログラマブルロジックを初めて使う人のために、DigilentのBasys 3ボードを選びました。

DigilentのBasys 3は、FPGA入門者向けのトレーナーボードで、XilinxのArtix-7デバイスの1つを中心に構成されています。Xilinxは、WebPACKと呼ばれる Vivado Design Suiteの無償版を提供しています。また、同社のウェブサイトで登録し、いくつかの基本情報を提供すれば、無期限の無償ライセンスが提供されることになっています。

始める前に

- もちろん、XilinxのVivado Design Suiteのダウンロードとインストールが必要です。対象となるプログラマブルロジックデバイスが対応していれば、無料のWebPACKバージョンでこのガイドを完遂することができます(作成にはWebPACKのリリース2015.4が使用されています)。無償ライセンスのインストールや設定についてヘルプが必要な場合は、Digilentが有用なガイドを提供しています。

- また、適切な開発ボードも必要です。まだお持ちでない場合は、DigilentのBasys 3ボードをご購入ください。資格のあるお客様は、Digi-Keyにお電話いただければ、アカデミック価格にてご提供いたします。

- Basys 3にはUSBケーブルが付属していませんので、正しいタイプの予備をお持ちでない方はBasys 3と一緒にご購入いただくか、より汎用性の高い魅力的なものがお好みの方はこちらをBasys 3と一緒にご購入ください。

- 外部JTAGプログラマや電源を必要とする開発ボードを使用する場合は、もちろんこれらも必要です。Basys 3はこれらの機能を内蔵していますが、他のハードウェアをお使いの場合は、お使いのハードウェアのマニュアルをご確認ください。

- JTAGプログラマや開発ボードをコンピュータに接続し、電源を入れ、必要なドライバをインストールする必要があります。

シンプルなスタート - 基本的なロジックとI/O

ここでは、3つのピンを入力、3つのピンを出力として構成し、その間に簡単なロジックを配置するという、極めてシンプルな構成から始めます。Basys 3の例では、基板の最初の3つのスイッチ(SW0~SW2)が入力に、最初の3つのLED(LD0~LD2)が出力に接続されます。

新規プロジェクトの作成

Vivadoを起動したら、起動ページから「Create New Project(新規プロジェクトの作成)」アイコンをクリックします。または、File(ファイル)→New Project(新規プロジェクト)を選択します。

New Projectウィザードが起動しますので、「Next >」ボタンをクリックして次に進みます。

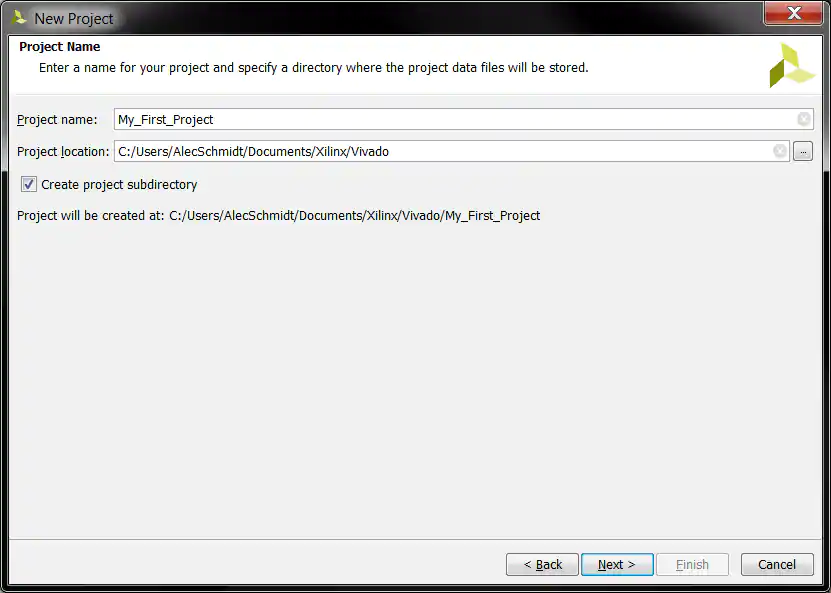

project name(プロジェクト名)を入力し、project location(プロジェクトの場所)を選択します。どちらにも「スペース」がないことを確認してください! 文字、数字、およびアンダースコアだけを使うのも悪くはないでしょう。必要であれば、ルートドライブにXilinx Vivadoプロジェクト用の新しいディレクトリを作成します(例:C:\Vivado)。「Create project sub-directory(プロジェクトのサブディレクトリを作成する)」のチェックボックスも常に選択します。こうすることで、プロジェクトごとにディレクトリができ、すっきりと整理され、トラブルを回避することができます。「Next >」ボタンをクリックして次に進みます。

「RTL Project」を選択し、「Do not specify sources at this time(現時点ではソースを指定しない)」チェックボックスを選択します。チェックボックスを選択しない場合、ウィザードは、VHDLまたはVerilogソースファイル、Vivado IPブロック、およびデバイスピンとタイミングコンフィギュレーション用の.XDC 制約ファイルなどの既存のアイテムをオプションで追加するためのいくつかの追加手順に進みます。この最初のプロジェクトでは、後で必要なアイテムを追加します。「Next >」ボタンをクリックして次に進みます。

プロジェクトで使用するデバイス品番に絞り込み、選択する必要があります。チップ上のマークを読むか、ボードのドキュメントを参照することで、品番を見つけることができます。Basys 3の場合、ボード上にあるのは Artix-7チップであり、表示されているフィルタは、図でハイライト表示されている正しいデバイスに到達するのに役立ちます。正しいデバイスを選択したら、「Next >」ボタンをクリックして次に進みます。

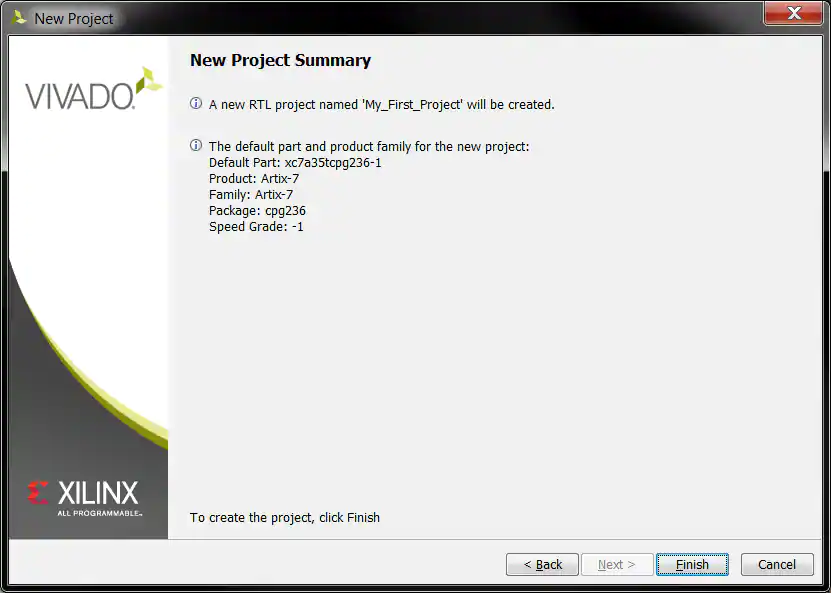

「Finish」ボタンをクリックすると、Vivadoは指定された通りにプロジェクトを作成するよう進めます。

基本的なプロジェクトのフローの実行

Vivado のプロジェクトウィンドウには多くの情報が含まれており、プロジェクトのステップを進めるにつれて、現在デザインのどのフェーズを開いているかで表示される情報が変わります。もし、特定のサブウィンドウやサブウィンドウタブが表示されない場合は、正しいデザインのフェーズではない可能性があるのでご留意ください。

画面左側の「Flow Navigator(フローナビゲータ)」では、プロジェクトの主要なフェーズが上から下へと自然な時系列で整理されています。フローの「Project Manager(プロジェクトマネージャ)」部分から始まりますが、画面上部のフローナビゲータの横にあるヘッダがこれを反映しています。このヘッダと、フローナビゲータの対応するハイライト表示されたセクションで、開いているデザインのフェーズがわかります。

プロジェクトマネージャ

プロジェクトの設定

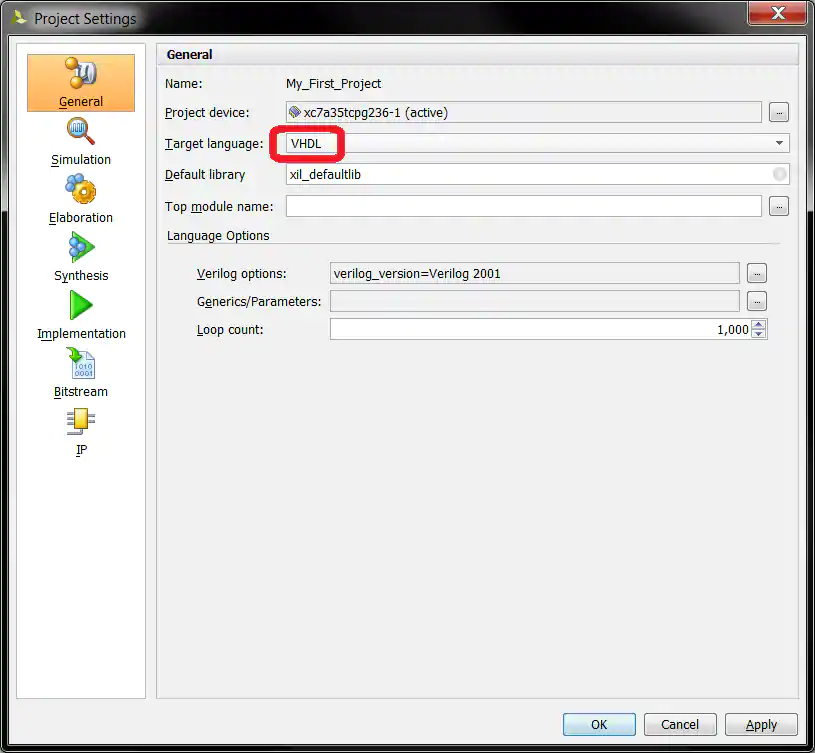

フローナビゲータのProject Managerフェーズにある「Project Settings(プロジェクト設定)」をクリックすることから始めます。

ここでは、プロジェクトフローのすべてのフェーズについて多くの設定が用意されていますが、とりあえず「General(一般)」のプロジェクト設定で「Target language(ターゲット言語)」のドロップダウンから「VHDL」を選択して「OK」ボタンをクリックします。

ソースの追加

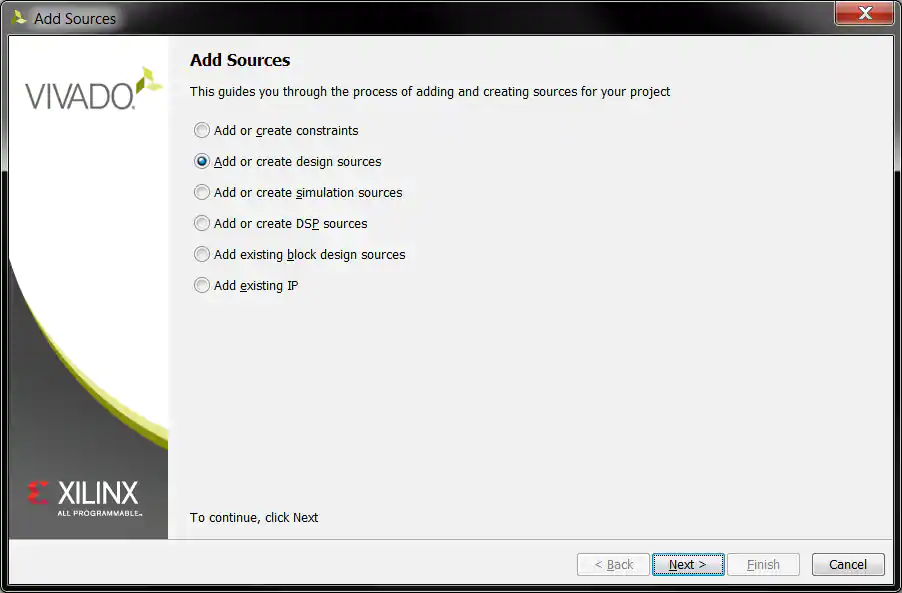

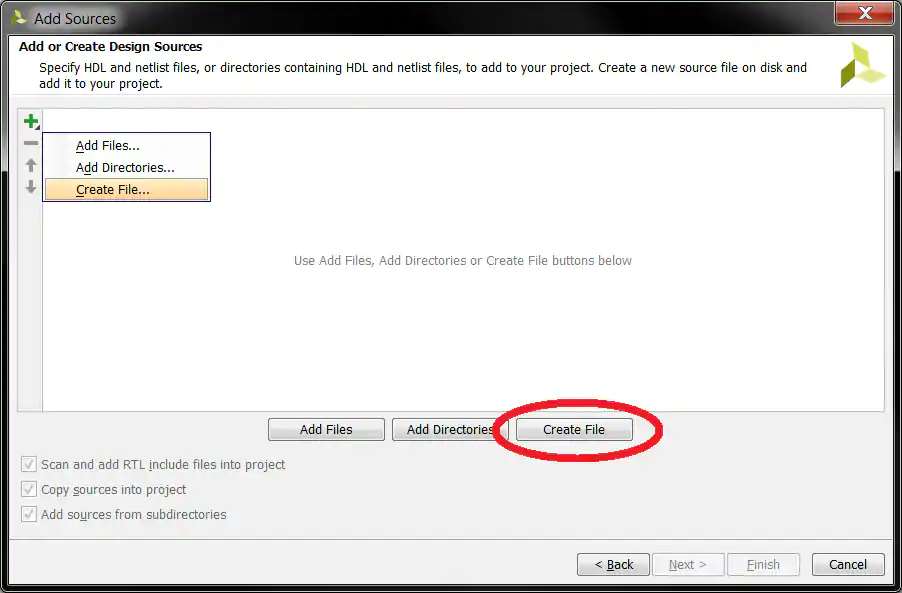

ここで、フローナビゲータのProject Managerフェーズにある「Add Sources(ソースの追加)」をクリックします。

「Add or create design sources(デザインソースの追加または作成)」を選択し、「Next >」ボタンをクリックします。

「Create File(ファイルを作成)」ボタンをクリックするか、左上の緑色の「+」マークをクリックして、そして「Create File…(ファイルを作成)」オプションを選択します。

「Create Source File」ポップアップで、適切なオプションが選択されていることを確認し、次に進むために「File name」に「Basic_Logic」と入力してください。終了したら「OK」ボタンをクリックします。

「ファイル名」は、有効なものであれば通常何でも入力できますが、「スペース」は絶対に入れないようにしてください!

「Finish」ボタンをクリックすると、Vivadoの「Define Module(モジュールの定義)」ウィンドウが表示されます。

モジュールの定義

「Define Module(モジュールの定義)」ウィンドウを使用すると、VHDLコードの一部を自動的に作成することができます。左上の緑色の「+」マークをクリックするか、次の空行をクリックすることで、「I/O Port Definitions(I/Oポートの定義)」を追加することができます。「Entity name」と「Architecture name」は、コード内で使用される対応するVHDL識別子となり、各「ポート名」に入力されたものも同様です。有効なVHDL識別子であれば、どれを使っても構いませんが、今回は次のように情報を入力してください。各ポートに適切な「Direction(入力/出力)」が設定されていることを確認します。完了したら「OK」ボタンをクリックします。

もし、ゼロから独自のコードを書きたい場合は、「Cancel」ボタンをクリックするだけで、Vivadoはプロジェクト内に全く白紙のVHDLソースファイルを作成します。「I/O Port Definitions」を定義せずに「OK」ボタンをクリックすると、Vivadoは基本的なVHDLコード構造を記述しますが、ポートの定義は空でコメントアウトされ、後でコメントを解除して記入するようコメントが出ます。

また、このポート名は、この例で使用するBasis 3ボードのスイッチやLEDのシルクスクリーンの参照指定子と一致していることに注意してください。これは、Basys 3を使用する人の便宜を図るためのもので、初心者に必須の要件ではありません。各名称は、単なる任意の識別子です。

生成されたVHDLソースファイルは、図のように「Design Sources」フォルダにあるプロジェクトに追加されます。それをダブルクリックすると、新しいタブで開いて表示/編集できます。ここにあるすべてのコードは、前の「モジュールの定義」ウィンドウで生成されたものです。この例では、「begin」と「end」のキーワードの間にある、ハイライトされた3行だけを手動で入力する必要があります。

その3行は、以下の通りです。

LD0 <= SW0;

LD1 <= SW1 and SW2;

LD2 <= SW1 or SW2;

上記の行は非常にシンプルです。このガイドはVHDLチュートリアルを意図したものではなく、どのような動作を期待すればよいかを理解するのに役立つ全くのVHDL初心者のためのものです。

- 1行目は、「SW0」入力を「LD0」出力(バッファ)に直接割り当てているだけです。

- 2行目は、入力「SW1」と「SW2」の論理積を「LD1」出力(ANDゲート)に割り当てています。

- 3行目は、入力「SW1」と「SW2」の論理和を「LD2」出力(ORゲート)に割り当てています。

その3行が正しく入力されたら、VivadoのトップのドロップダウンメニューからFile → Save Fileを選択します。

RTL解析

Elaborated Designを開く

ここで、フローナビゲータのRTL Analysisフェーズにある「Open Elaborated Design」をクリックします。また、ポップアップが表示される場合がありますが、その場合は「OK」ボタンをクリックしてください。Vivadoは少しの作業を行い、その後Elaborated Designを開きます。

フローナビゲータで「RTL Analysis」フェーズがハイライト表示され、その横のヘッダが「Project Manager」から「Elaborated Design」に変わり、「Elaborated Design」と関連するウィンドウが表示されていることが分かります。フローナビゲータで「Project Manager」と「RTL ARTL Analysis」のフェーズを交互にクリックすると、それに応じてヘッダとウィンドウが変化するのがわかります。

回路図を表示

フローナビゲータのRTL Analysisフェーズの下にある「Schematic(回路図)」をクリックすると、以前に記述したVHDLの回路図が表示されるタブが表示されます。

デバイスのピン配列

Elaborated Designを開いた状態で、実際にプログラマブルロジックデバイスのピン配列を行うことができます。トップバーのドロップダウンから「I/O Planning」ビューを選択し、下部にある「I/O Ports」タブが表示されていることを確認し、クリックして利用可能なすべてのポートを展開し表示します。

ポート名と方向(入力/出力)は、以前に入力したVHDLコードと一致します。プログラマブルロジックデバイスの有効な物理的ピン配列を与えるために、それぞれについて「Site」をタイプ入力するか、ドロップダウンから選択する必要があります。同様に、選択した各ピンのI/Oバンクのパワーレールに合わせて、適切な「I/O Std」を割り当てる必要があります。

Basys 3ボードを使用する場合、各ポートに表示されるピン「Site」の割り当ては、便宜上ボードのシルクスクリーンに合わせ、「I/O Std」の選択はすべて「LVCMOS33」にしてください。

すべてが正しく入力されたら、Vivadoのトップのドロップダウンメニューから File → Save Constraintsを選択します。

Constraints Fileの作成

「Save Constraints」ポップアップで表示されるオプションが選択されていることを確認し、「File name」に「Basic_Logic」を入力します。終了したら「OK」ボタンをクリックします。

「ファイル名」は有効なものであれば通常何でも入力できますし、この例のようにHDLファイル名と一致させる必要はありませんが、「スペース」は絶対に入れないようにしてください!

「Sources」ウィンドウの「Sources」サブタブ内でconstraints fileをダブルクリックすると、constraints fileを表示し、手動で編集することができます。閲覧のために開きますが、今は編集しないでおいてください。

合成と実装(Synthesis and Implementation)

ここで、フローナビゲータのSynthesisフェーズで「Run Synthesis(合成の実行)」をクリックします。Vivadoが終了するまでには、ある程度の時間がかかります。「Synthesis Completed」のポップアップが表示されたら、「Run Implementation」を選択し、「OK」ボタンをクリックします。そうでない場合は、代わりに、合成の完了後にフローナビゲータのImplementationフェーズで「Run Implementation(実装の実行)」をクリックします。Vivadoが終了するまでには、また少し時間がかかります。

プログラムとデバッグ(Program and Debug)

ビットストリームの生成(Generate Bitstream)

「Implementation Completed」ポップアップが表示されたら、「Generate Bitstream」を選択し、「OK」ボタンをクリックします。インプリメンテーションが完了した後、フローナビゲータのProgram and Debugフェーズで「Generate Bitstream(ビットストリームの生成)」をクリックします。

「Bitstream Generation Completed」ポップアップが表示されたら、「Open Hardware Manager」を選択して、「OK」ボタンをクリックします。そうでない場合は、ビットストリームの生成が完了した後、フローナビゲータのProgram and Debugフェーズで「Open Hardware Manager(ハードウェアマネージャ)を開く」をクリックすることができます。

ターゲットを開く(Open Target)

ここで、フローナビゲータのProgram and Debugフェーズにある「Open Target(ターゲットを開く)」をクリックし、表示されたメニューから「Open New Target(新しいターゲットを開く)…」をクリックします。JTAGプログラマや開発ボードをコンピュータに接続し、電源を入れ、必要なドライバをインストールした上で、作業を続けてください。

Open New Hardware Target(新しいハードウェアターゲットを開く)ウィザードが起動しますので、「Next >」ボタンをクリックして次に進みます。

ドロップダウンから「Local server (target is on local machine) 」を選択し、「Next >」ボタンをクリックして次に進みます。Vivadoは、ローカルマシンに接続されている有効なターゲットデバイスを検索するためにしばらく動作します。

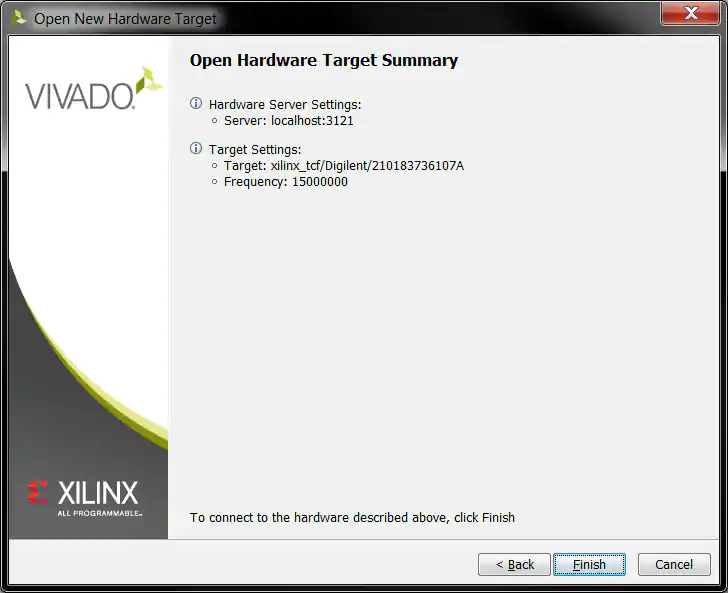

うまくいけば、ここに示したような、特定のハードウェアに適合するものが表示されます。JTAGのハードウェアターゲットとプログラマブルロジックデバイスを選択し、「Next >」ボタンをクリックします。なお、「JTAG Clock Frequency(JTAGクロック周波数)」を変更するオプションもありますが、最初はデフォルトの設定で、必要な場合のみ後で調整するのが合理的です。

「Finish」ボタンをクリックすると、Vivadoは指定されたハードウェアへの接続を試みます。

デバイスのプログラム

次に、フローナビゲータのProgram and Debugフェーズにある「Program Device(デバイスのプログラム)」をクリックし、表示されるメニューから特定のデバイスをクリックします。

表示された「Program Device」ポップアップには、生成したビットストリームファイルのファイルパスが自動的に入力されているはずです。「Enable end of startup check(スタートアップの終了チェックを有効にする)」チェックボックスを選択し、「プログラム」ボタンをクリックします。Vivadoはしばらく動作しますが、成功すれば、すべてが終了した時点でデバイスがプログラムされ、その正しい動作を確認する準備が整います。

Basys 3をお使いの方は、スイッチ(SW0~SW2)を切り替えて、先に説明したLED(LD0~LD2)が正しく動作することを確認してください。