製品の入手について

MachXO2ブレイクアウト基板のオリジナル版はLCMXO2-1200ZE-1TG144C CPLD(Complex Programmable Logic Device)を搭載していましたが、新バージョンではLCMXO2-7000HE-4TG144Cに置き換わりました。

新バージョンのMachXO2ブレイクアウト基板(LCMXO2-7000HE-B-EVN)は、Digi-Keyからこちらで入手可能です。

旧バージョンのMachXO2ブレイクアウト基板(LCMXO2-1200ZE-B-EVN)は、Digi-Keyの在庫がある限り、こちらで入手できます。

チュートリアル用Verilogコード

blinking_led.v (3.7 KB)

はじめに

注:このページの情報は主にeeWikiの「LOGIC 」セクション内のLattice Diamond and MachXO2 ブレイクアウト基板のチュートリアルから引用しています。設計コンセプトは、VerilogとVHDLの両方の実装に関連します。

このLattice Diamondソフトウェア(バージョン2.0.1)の解説は、MachXO2ブレイクアウト基板評価キット用の簡単なプロジェクトを作成する手順を説明しています。このプロジェクトでは、4 - 8ビットのデータエンコーダで制御されたパターンで1バイト配列のLEDを点滅させる回路を簡単に作成します。発振器は133MHzに設定されており、「N」パラメータまたは発振器周波数を変更することにより、ブリンク周波数を調整することができます。デフォルトのカウンタ設定は28ビットです。どちらのバージョンのキットでも動作します。新しいプロジェクトの開始、コード入力、内蔵発振器の使用、コンパイル、ピン割り当て、および基板のプログラミングなどのトピックがあります。シミュレーションについては、別途チュートリアルがあります。このチュートリアルで使用するボードは、MachXO2ブレイクアウト基板(LCMXO2-7000HE、Digi-Key品番220-2625-ND、これは最近LCMXO2-1200ZE-B-EVN、Digi-Key品番220-1298-NDから置き換わりました)です。これらの基板は、いずれも低コストのプログラマブルロジックデバイス(PLD)開発ボードです。MachXO2は、ASICゲートをベースとしたハード化された組み込み機能ブロック(EFB)を搭載した低消費電力FPGAです。

アプリケーション

新規プロジェクトを作成する

新しいプロジェクトを作成するには、File → New → Project…の順に選択すると、新規プロジェクトウィザードが起動します。Nextをクリックします。図1のようにプロジェクト名(Project Name)と場所(Location)を入力し、Nextをクリックします。

図1.新規プロジェクトの名称と場所

このプロジェクトでは、既存のソースファイルは使用しません。Nextをクリックします。

デバイスファミリをMachXO2、デバイスをLCMXO2-7000HEまたはLCMXO2-1200ZE(お持ちのボードのバージョンによる)、パッケージタイプをTQFP144、パフォーマンスグレードを4(7000HE使用時)または1(1200ZE使用時)、そして動作条件をCommercialに指定してください。ドロップダウンリストに適切なオプションを表示するには、これらの基準のいくつかを先に選択する必要があります。図2に示すように、部品名テキストボックスにLCMXO2-7000HE-4TG144CまたはLCMXO2-1200ZE-1TG144Cという完全な品番 が表示されます。Nextをクリックします。Finishをクリックします。

図2.デバイスを選択する

内蔵発振器のインスタンス化とVerilogコードの入力

新しいソースファイルを作成するには、File → New → File…を選択します。図3に示すように、カテゴリはSource Files、そしてSource filesタイプはVerilog Filesを選択します。新しいファイルに名前を付けて、Newをクリックしま**

図3.新しいVerilogソースファイルを作成する

発振器モジュールは、同梱のblinking_led.vファイルにあるように、トップレベルのアーキテクチャ内でインスタンス化する必要があります。公称周波数は、下記図4に示すように、モジュール「defparam」のインスタンス化で定義することができます。このデザインは133MHzで動作しています。

図4.Verilogによる発振器のインスタンス化コード例

トップレベルのVerilogラッパーは、「blinking_led」と呼ばれるモジュールです。下記図5のコード例で見ることができます。

図5.トップレベルのモジュール

LEDのタイミングに使用されるカウンタは、図6の「always」ブロックに見ることができます。

図6.カウンタ用「Always」ブロック

このモジュールの最後の要素は、カウンタの最上位ニブルを、8ビットLEDアレイで表現する1バイトのパターンにエンコードする「always」ブロックです。これは、図7に示すコード例のようになります。

図7.4 - 8ビットデータエンコーダのROM化

ピン割り当てとコンパイル

Processペインを選択し、ProcessペインのTranslate Designをダブルクリックすると、合成とトランスレーションを実行します。これを図8に示します。

図 8.ピンアサイン前にデザインのトランスレートをする

Tools → Spreadsheet Viewを選択します。Spreadsheet Viewの下部にあるPin Assignmentsタブをクリックします。ピン107が表示されるまで下にスクロールします。107ピンのSignal Name欄でダブルクリックします。図9のようなAssign Signalsダイアログボックスが表示されます。

図9.Spreadsheet Viewによるピンの割り当て

led0信号を選択し、Assign Signalsをクリックして、それらを107, 106, 105, 104, 100, 99, 98, および97ピンに割り当てます。107番ピンはMachXO2ブレイクアウトボードのLED D8に接続され、その他はボード上のD7~D1にそれぞれ接続されています。

Processペインに戻り、Export FilesのJEDEC Fileにチェックを入れます。Export Filesをダブルクリックして、マッピング(Map)、配置配線プロセス(Place & Route)を行い、JEDECプログラミングファイルを作成します。変更したファイルを保存するかどうか尋ねられたら、保存してください。図10は、成功した結果を示しています。

図10.合成、マッピング、配置配線、およびJEDECファイル作成に成功

CPLDをプログラミングする

MachXO2ブレイクアウト基板をUSBケーブルでパソコンに接続します。

Tools → Programmerを選択します。図8に示すように、Programmer: Getting Startedダイアログボックスが表示されます。OKをクリックします。

図 11.Getting Startedダイアログボックスを開き、プログラマを設定する

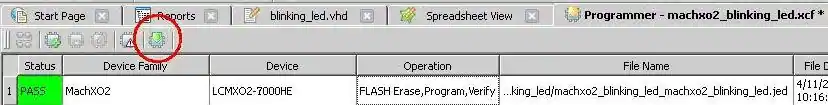

プログラムアイコンをクリックします。デバイスがプログラムされます。完了すると、図12に示すように、Status表示が緑色に変わります。8個のLEDが対称的なパターンで点滅し、各LEDの点滅時間は約250msです。

図12.PLDプログラミングが正常に終了

機能、制限、および変更点

このチュートリアルの開発にはLattice Diamondバージョン2.0.1とSynopsisのサポートソフトウェア(Synplify Pro)が使用されています。Lattice Diamondは、サードパーティの合成やシミュレーション用ソフトウェアを採用することで、スタンドアロン開発環境として使用することができます。

まとめ

Lattice DiamondソフトウェアとMachXO2ブレイクアウト基板の今回の解説は、Verilogハードウェア記述言語を用いて、これらのツールで簡単なプロジェクトを作成するための基本的なステップを紹介しています。

補足説明

さらなる設計サポート、製品チュートリアル、アプリケーションノート、ユーザーズガイド、およびその他の資料は、Latticeのウェブサイトでご覧いただけます。https://www.latticesemi.com/ja-JP

付録

MachXO2 Breakout Board Tutorial with HDLの完全版は、こちらからダウンロードできます。

デフォルトの周波数は2.08MHzです。サポートされている周波数(単位:MHz、「blinking_led」モジュールのコメントに記載)は、下の図13に示しています。

図13.内部発振器対応周波数