可用性

MachXO2 分接板的原始版本採用 LCMXO2-1200ZE-1TG144C CPLD,現已在新版本的板上替換為 LCMXO2-7000HE-4TG144C。

DigiKey 亦有提供新版本的 MachXO2 分接板(LCMXO2-7000HE-B-EVN) ,請點擊此處。

教學的 Verilog 程式碼

blinking_led.v (3.7 KB)

介紹

注意:本頁面資訊主要取自 eeWiki 中「LOGIC」部分的 Lattice Diamond 和 MachXO2 分接板教學頁面;設計概念實際應用於 Verilog 和 VHDL。

本 Lattice Diamond 軟體(版本 2.0.1)的介紹將指導您如何為 MachXO2 分接板評估套件建立一個簡單的項目。該專案僅建立了一個電路,用於以由 4-8bit 資料編碼器控制的模式閃爍一個單字節 LED 陣列。振盪器設定為 133MHz;閃爍頻率可以透過更改 N 參數或振盪器頻率來調整。預設計數器設定為 28-bit。它適用於任何版本的套件。主題包括建立新專案、程式碼輸入、使用內部振盪器、編譯、引腳分配以及對電路板進行程式設計。另外一個單獨的教學介紹仿真。本教學中使用的開發板是 MachXO2 分接板(LCMXO2-7000HE,DigiKey 零件編號 220-2625-ND,最近取代了 LCMXO2-1200ZE-B-EVN,DigiKey 零件編號 220-1298-ND)。這兩款開發板均為低成本可程式邏輯元件(PLD)開發板。 MachXO2 是一款低功耗 FPGA,具有基於 ASIC 閘的強化嵌入式功能塊(EFB)。

應用

建立新專案

若要建立新項目,請選擇「檔案」→ 「新建」→ 「項目…」,然後啟動「新建專案精靈」。點選「下一步」。輸入項目名稱和位置(如圖 1 所示),然後點選「下一步」。

圖 1. 新項目名稱和位置

此項目不使用現有原始檔。點選「下一步」。

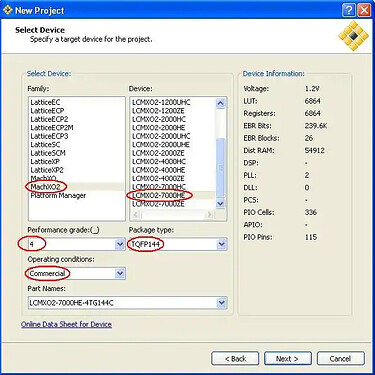

將裝置系列指定為 MachXO2,裝置型號為 LCMXO2-7000HE 或 LCMXO2-1200ZE(取決於您使用的開發板版本),封裝類型為 TQFP144,性能等級為 4 (如果使用 7000HE)或 1(如果使用 1200ZE),工作條件為「商業級」。必須先選擇其中一些條件,才能在下拉清單中填入正確的選項。完整的裝置型號 LCMXO2-7000HE-4TG144C 或 LCMXO2-1200ZE-1TG144C 將顯示在裝置名稱文字方塊中,如圖 2 所示。點選「下一步」。點選「完成」。

圖 2. 選擇設備

實例化晶片上振盪器和 Verilog 編碼輸入

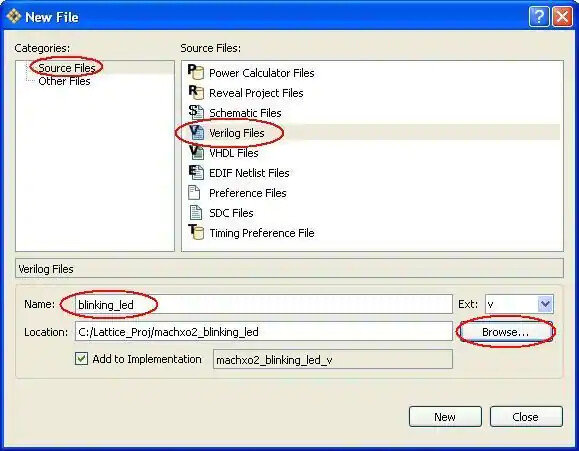

若要建立新的來源文件,請選擇「文件」→「新建」→「文件…」。選擇「原始檔」類別和「Verilog 檔案」類型,如圖 3 所示。為新檔案命名,然後點選「新建」。

圖 3. 建立新的 Verilog 原始檔

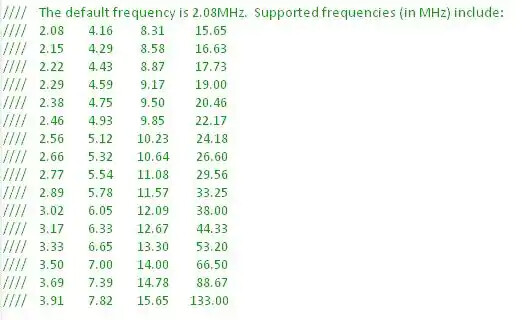

振盪器模組必須在頂層架構中實例化,如隨附的 blinking_led.v 檔案所示。標稱頻率可以在模組「defparam」實例中定義,如下圖 4 所示。本設計運作頻率為 133MHz。

圖 4. Verilog 振盪器實例化程式碼片段

頂層 Verilog 包裝器是一個名為「blinking_led」的模組。它可以在下方圖 5 的程式碼片段中看到。

圖 5. 頂層模組

用於 LED 計時的計數器位於圖 6 的「always」模組中。

圖 6. 計數器的「Always」模組

模組的最後一部分是「Always」模組,用於將計數器的最高有效半位元組編碼為 8-bit LED 陣列上顯示的 1bit模式。這在圖 7 中的程式碼片段中可見。

圖 7. 4 至 8-bit資料編碼器推斷為 ROM

引腳分配和編譯

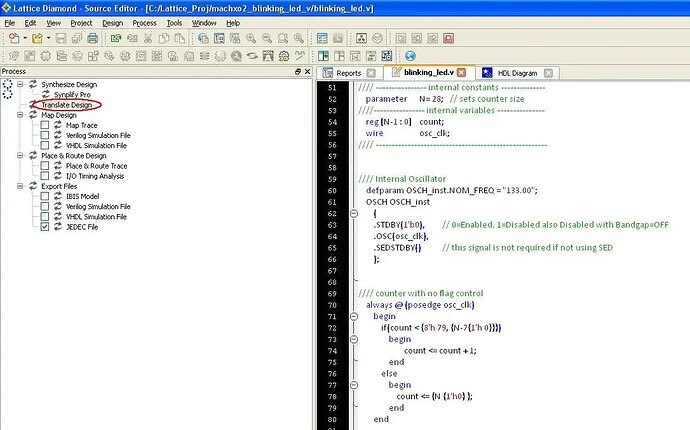

選擇流程面板,然後雙擊「Translate Design」進行綜合和轉換。如下圖 8 所示。

圖 8. 引腳分配前轉換設計

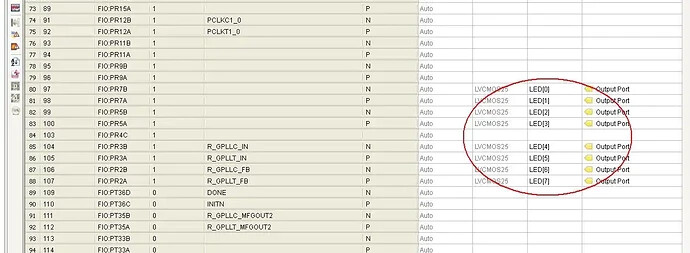

接下來,選擇「工具」→「試算表視圖」。點擊試算表視圖底部的「引腳分配」標籤。向下捲動直到出現引腳 107。雙擊引腳 107 的「信號名稱」列。此時將出現「分配訊號」對話框,如圖 9 所示。

圖 9. 使用試算表視圖進行引腳分配

選擇 led0 訊號,然後點擊「分配訊號」,將其分配給引腳 107、106、105、104、100、99、98 和 97。引腳 107 連接到 MachXO2 分線板上的 LED D8,其他引腳分別透過電路板上的 D1 連接。

返回流程面板,選取「匯出檔案」下的「JEDEC 檔案」。雙擊「匯出檔案到對應、佈局和佈線」,然後建立 JEDEC 程式設計檔案。如果系統提示您儲存修改後的文件,請儲存。圖 10 顯示了成功的結果。

圖 10. 成功完成綜合、對應、佈局佈線以及 JEDEC 文件建立

CPLD 編程

透過 USB 連接線將 MachXO2 分接板插入電腦。

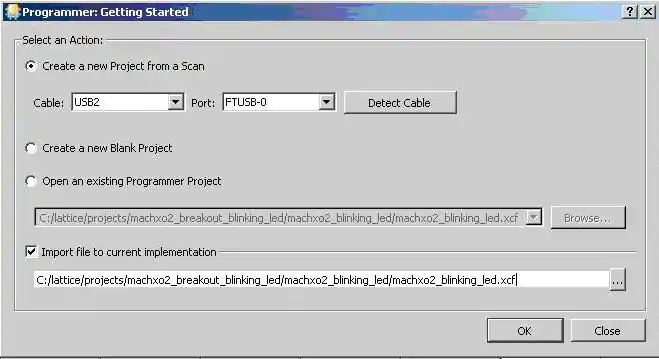

選擇「工具」→「編程器」。 「程式設計器:開始」對話方塊將會打開,如圖 11 所示。點選「確定」。

圖 11. 開啟「開始」對話方塊設定編程器

點擊「編程」圖示。設備將開始編程。編程完成後,狀態指示燈將變為綠色,如圖 12 所示。 8 個 LED 將以對稱模式閃爍,每個 LED 閃爍持續時間約為 250ms。

圖 12. 對 PLD 進行程式設計並成功

功能、限制和變更

本教學使用 Lattice Diamond 2.0.1 版本開發,並結合 Synopsis 的支援軟體(Synplify Pro)。Lattice Diamond 可作為獨立的開發環境,與第三方綜合和模擬軟體搭配使用。

結論

本教學介紹了 Lattice Diamond 軟體和 MachXO2 分接板,並示範了使用這些工具和 Verilog 硬體描述語言建立簡單專案的基本步驟。

附加資料

更多設計支援、產品教學、應用筆記、使用者指南及其他文檔,請訪問Lattice網站:Lattice Semiconductor | The Low Power FPGA Leader

附錄

完整的 MachXO2 分接板教學(含 HDL 程式碼)可在此下載。

預設頻率為 2.08MHz。支援的頻率(單位為 MHz,可在「blinking_led」模組的註解中找到)如下圖 13 所示。

圖 13. 內部振盪器支援的頻率