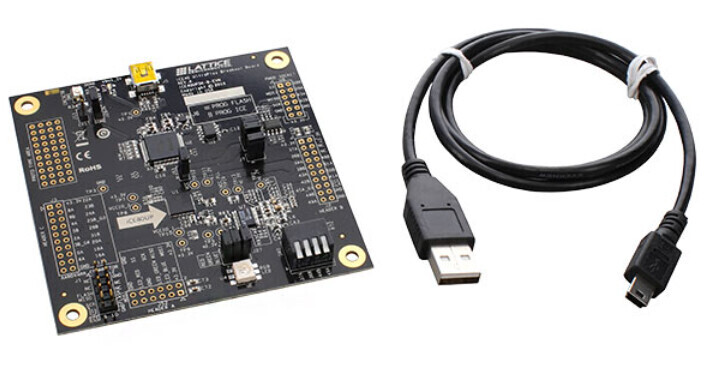

El presente artículo presenta un ejemplo de una sencilla implementación de un Moore Finite State Machine (FSM) usando el mecanismo de APIO para la plataforma Lattice ICE40 FPGA UltraPlus Breakout Board. Si es necesario se refiere al previo artículo que define la instalación de la herramienta APIO. La plataforma Lattice ICE40 FPGA UltraPlus Breakout Board es una excelente herramienta de desarrollo,

Una máquina de estados finitos (FSM) del tipo Moore se muestra a continuación usando el sistema APIO, usando el SystemVerilog HDL en esta plataforma. El sistema APIO tiene incluido el SystemVerilog HDL. El diagrama de estados para el demo de la máquina de estados finitos es el siguiente,

El diagrama genérico de la máquina de estados finitos tipo Moore es el siguiente,

El diagrama de estados ilustra la definición de los estados y las relevantes transiciones basadas en el estado de la entrada discreta next al sistema. Esta señal next de entrada esta conectada a un interruptor disponible en la plataforma que se usa para parar la transición del estado en cualquier momento dentro del FPGA (especificamente muestreando con el reloj interno de 12MHz pero dividido a un periodo de aproximadamente un segundo). El reloj de 12 MHz se dividio con un divisor auxiliar para que con el ojo humano se puedan percibir los cambios de las transiciones de estos estados. La máquina de estados finitos tipo Moore tiene las salidas r,g,b que estan conectadas al LED RGB en el Lattice ICE40 FPGA UltraPlus Breakout Board en este demo. Cada estado representa un color RED, BLIE y GREEN (Rojo, Azul y Verde) en este orden en particular y continuará cambiando como se muestra en el diagrama a menos que el interruptor next sea deasctivado. En esta situación, las transiciones paran y la máquina de estados finitos tipo Moore permanece en un estado fijo (color fijo). Una provición para un reseteo asincrónico se incluyo para que el sistema regrese al color rojo cuando se oprima el otro interruptor conectado que sirve de reseteo. El color rojo es el estado de reseteo. Los sigueintes archivos relevantes son usados en este demo, el primero es el SystemVerilog HDL top.sv,

//Digikey Coffee Cup SystemVerilog HDL Moore State Machine

module top(input [3:0] SW, input clk, output LED_R, output LED_G, output LED_B);

Moore fsm_sm1(.clk(counter[23]),.reset(SW[0]), .next(SW[1]), .r(LED_R), .g(LED_G), .b(LED_B));

//Auxiliary counter to divide the clock to be used in the Moore State Machine Demo

reg [23:0] counter;

initial begin

counter = 0;

end

always_ff @(posedge clk)

begin

counter <= counter + 1;

end

endmodule

El SystemVerilog HDL para la máquina de estados finitos tipo Moore denominada moore_fsm.sv es el siguiente,

//Digikey Coffee Cup SystemVerilog HDL Moore State Machine

module Moore(

input logic clk,

input logic reset,

input logic next,

output logic r, g, b

);

typedef enum logic [1:0] {RED, BLUE, GREEN} statetype;

statetype state, nextstate;

// state register

always_ff @(posedge clk, posedge reset)

if (reset)

state <= RED;

else

state <= nextstate;

// next state logic

always_comb

case (state)

RED: if (next) nextstate = BLUE;

else nextstate = RED;

BLUE: if (next) nextstate = GREEN;

else nextstate = BLUE;

GREEN: if (next) nextstate = RED;

else nextstate = GREEN;

default: nextstate = RED;

endcase

// output logic

assign r = ~(state == RED & state != GREEN & state != BLUE);

assign b = ~(state != RED & state != GREEN & state == BLUE);

assign g = ~(state != RED & state == GREEN & state != BLUE);

endmodule

Todos los SystemVerilog HDL del projecto APIO y los archivos de definición del directorio son los sigueintes,

├── apio.ini

├── moore_fsm.sv

├── pinout.pcf

└── top.sv

El archivo apio.ini define el projecto APIO como sigue,

; DigiKey Cofffe Cup Apio project file.

[env:default]

; Board id.

board = ice40-up5k

; Top module name (top.sv)

top-module = top

El archivo llamado pinout.pcf define los pins así,

# DigiKey Cofffe Cup Apio pins definitions file

set_io LED_R 41

set_io LED_G 40

set_io LED_B 39

set_io SW[0] 23

set_io SW[1] 25

set_io SW[2] 34

set_io SW[3] 43

set_io clk 35

El lint de APIO lint se usa para verificar errores,

Digikey_Coffee_Cup # apio lint

Entonces se procede a construir el projecto así,

Digikey_Coffee_Cup # apio build

El sistema APIO provee una lista de los recursos totales usados con este comando,

Digikey_Coffee_Cup # apio report

Esto reporta la utilización como sigue,

FPGA Resource Utilization

┌──────────────────┬────────┬──────────┬─────────┐

│ RESOURCE │ USED │ TOTAL │ UTIL. │

├──────────────────┼────────┼──────────┼─────────┤

│ ICESTORM_DSP │ │ 8 │ │

│ ICESTORM_HFOSC │ │ 1 │ │

│ ICESTORM_LC │ 32 │ 5280 │ 0% │

│ ICESTORM_LFOSC │ │ 1 │ │

│ ICESTORM_PLL │ │ 1 │ │

│ ICESTORM_RAM │ │ 30 │ │

│ ICESTORM_SPRAM │ │ 4 │ │

│ IO_I3C │ │ 2 │ │

│ SB_GB │ 2 │ 8 │ 25% │

│ SB_I2C │ │ 2 │ │

│ SB_IO │ 8 │ 96 │ 8% │

│ SB_LEDDA_IP │ │ 1 │ │

│ SB_RGBA_DRV │ │ 1 │ │

│ SB_SPI │ │ 2 │ │

│ SB_WARMBOOT │ │ 1 │ │

└──────────────────┴────────┴──────────┴─────────┘

Clock Information

┌────────────────┬───────────────────┐

│ CLOCK │ MAX SPEED [Mhz] │

├────────────────┼───────────────────┤

│ clk │ 79.74 │

├────────────────┼───────────────────┤

│ counter[23]_ │ 232.23 │

└────────────────┴───────────────────┘

Run 'apio report --verbose' for more details.

========================= [SUCCESS] Took 0.81 seconds ==========================

Para ver la gráfica de la configuración de este demo se usa el siguiente comando,

Digikey_Coffee_Cup # apio graph

Esto genera un archivo .svg que contiene detalles de la configuración del FPGA así,

En este momento hay que asegurarse de que los “jumpers” en la plataforma Lattice ICE40 FPGA UltraPlus Breakout Board son conectados para programar el “FLASH” (Ver previo artículo). Una vez completado, se procede a programar la plataforma FPGA como sigue,

Digikey_Coffee_Cup # apio upload

El siguiente video muestra la máquina de estados finitos tipo Moore ejecutando el demo de las transiciones de los colores RED, BLUE and GREEN (Rojo, Azul y Verde), y cuando se oprime el botón del interruptor next para completamente en el color que se encuentre de lo contrario conitnua por el próximo estado definido en el diagrama.

Se ha completado la demostración del sistema APIO implementando la máquina de estados finitos tipo Moore en SystemVerilog HDL para la plataforma Lattice FPGA ICE40 UltraPlus Breakout Board. La plataforma Lattice FPGA ICE40 UltraPlus Breakout Board es una excelente, económica, con un area de prototipo en la plataforma que se puede usar para otros circuitos externos en muchas aplicaciones, y está disponible en DigiKey.

Que tenga un buen día.

Este artículo está disponible en inglés aquí.

This article is available in english here.