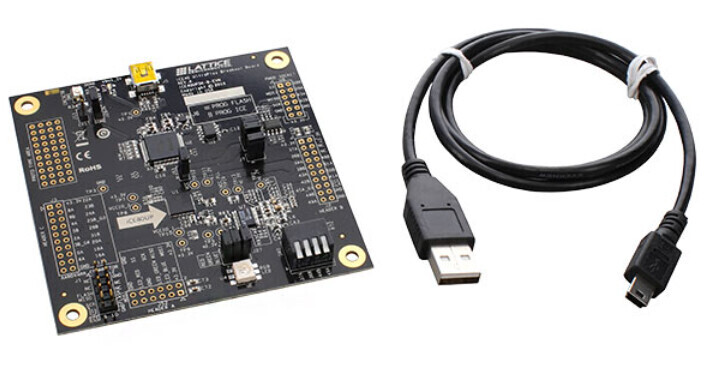

En el previo artículo se ha cubierto una máquina tipo Moore de estados finitos usando el mecanismo APIO para el Lattice ICE40 FPGA UltraPlus Breakout Board, en este artículo se va a usar el SystemVerilog HDL para demonstrar una máquina de estados finitos tipo Mealy.

Por favor se refiere al previo artículo que presenta la instalación del sistema APIO. La plataforma Lattice ICE40 FPGA UltraPlus Breakout Board es una herramienta excelente de desarrollo.

Una máquina tipo Moore de estados finitos usando el mecanismo APIO es implementada usando SystemVerilog HDL para esta plataforma. El sistema APIO ya permite el apoyo del SystemVerilog HDL. El diagrama de de estados finitos se muestra a continuación,

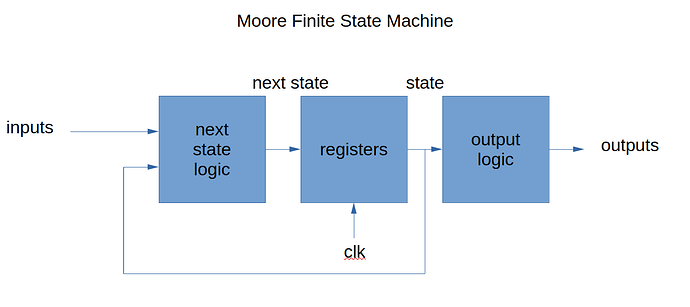

Contrario al previo Moore FSM que tiene 3 estados (RED, BLUE, GREEN), donde sus salidas dependen solamente de la codificación interna de la máquina de estados finitos solamente derivado de los estados internos de los flip flops, esto contiene los estados de los registros de la máquina de estados finitos, es la memoria interna de la máquina) El Mealy FSM usa la entrada next y su estado presente como la forma de controlar sus salidas r,g,b para alimentar el RGB LED en la plataforma. Aquí está el diagrama de bloque de la máquina tipo Moore para ilustrar la diferencia claramente,

En el diagrama previo, el Moore FSM deriva sus salidas solamente de los registros internos que representan el estado presente usando lógica combinacional. En contraste, la máquina Mealy FSM usa sus entradas (Ver linea roja en el diagrama) mas la codificacion presente en la salida de los registros como se muestra en el próximo diagram de bloque,

En general, la codificación interna se puede seleccionar como sea necesario dentro del proceso clásico del diseño de la máquina de estaods finitos. Hay distintos estilos dependiendo los requisitos de la aplicación (por ejemplo: secuencial, Gray, Johnson, One-Hot). La codificación One-Hot es tipicamente usado en FPGA donde hay abundancia de muchos flip-flops disponible. La codificación del tipo secuencial y Gray son usadas tipicamente en los CPLD’s y en los compactos ASIC’s donde no son abundantes. El compilador de sintesis del SystemVerilog HDL tiene 2 opciones, una es que se especifique por el usuario (user) y el otro (auto) que deja que el compilador selecione la codificación en base al artefacto que se desea usar.

Una caracteristica tipica de la máquina de estados finitos tipo Meal, es que puede producir mas condiciones de salida, comparado una máquina de tipo Moore, para un mismo numero de estados, porque incluye la entrada asincrónica next usada en la salida usando lógica combinacional. Usando la misma linea, si es necesario, el Moore FSM puede algunas veces puede ser reducida (convertida) a un Mealy FSM que puede tener menos número de estados depedendiendo si se pueden mezclar los estados (No posible en todas ocaciones)

El previo diagrama de estados de Mealy FSM incluye las definciones de los estados, las relevantes transciones basadas en la entrada next a el sistema. Esta señal discreta llamadanext está conectada a un interruptor en la plataforma que se usa para controlar el color de salida en cualquier momento en el FPGA. El reloj de 12 MHz es reducido en frecuencia con un dividsor auxiliar para que se puedan percibir las transiciones por el ojo humano en la plataforma. Las salidas del Mealy FSM son r, g, b determinadas de los estados del Mealy FSM (similar al Moore FSM) pero incluyendo la entrada next via lógica combinacional, que se usa para definir el color del RGB LEDen el Lattice ICE40 FPGA UltraPlus Breakout Board en este demo. Cada estado representa los colores RED, BLUE and GREEN para las transciones pero no para el color actual cuando la señal discreta esta activada next. Cuando la entrada next esta desactivada, se mantiene en ese estado, y salida esa color amarillo (r=1, g=1, b=0) para todos los estados en el diagram de estados Mealy.

Una provición de reseteo aincrónico está presente en el sistema para que el estado de reseteo sea el RED. La salida RGB LEDes amarilla en todos los estados y se mantien ahi hasta que la entrada next sea desactivada (Ver previo diagram de estados). Los siguientes archivos relevantes usados para este demo, el primero es el SystemVerilog HDL top.sv system,

//Digikey Coffee Cup SystemVerilog HDL Mealy State Machine

module top(input [3:0] SW, input clk, output LED_R, output LED_G, output LED_B);

Mealy fsm_sm1(.clk(counter[23]),.reset(SW[0]), .next(SW[1]), .r(LED_R), .g(LED_G), .b(LED_B));

//Auxiliary counter to divide the clock to be used in the Mealy State Machine Demo

reg [23:0] counter;

initial begin

counter = 0;

end

always_ff @(posedge clk)

begin

counter <= counter + 1;

end

endmodule

EL archivo SystemVerilog HDL para la máquina de estados finitos tipo Mealy se llama mealy_fsm.sv,

//Digikey Coffee Cup SystemVerilog HDL Mealy State Machine

module Mealy(

input logic clk,

input logic reset,

input logic next,

output logic r, g, b

);

typedef enum logic [1:0] {RED, BLUE, GREEN} statetype;

statetype state, nextstate;

// state register

always_ff @(posedge clk, posedge reset)

if (reset)

state <= RED;

else

state <= nextstate;

// next state logic

always_comb

case (state)

RED: if (next) nextstate = BLUE;

else nextstate = RED;

BLUE: if (next) nextstate = GREEN;

else nextstate = BLUE;

GREEN: if (next) nextstate = RED;

else nextstate = GREEN;

default: nextstate = RED;

endcase

// output logic (not simplified)

assign r = ~( next&(state == RED & state != GREEN & state != BLUE) | ~next&(1) );

assign b = ~( next&(state != RED & state != GREEN & state == BLUE) | ~next&(0) );

assign g = ~( next&(state != RED & state == GREEN & state != BLUE) | ~next&(1) );

endmodule

Los archvio relevantes de SystemVerilog HDL y el projecto APIO son los siguientes,

├── apio.ini

├── mealy_fsm.sv

├── pinout.pcf

└── top.sv

El archivo apio.ini que define el projecto APIO es,

; DigiKey Cofffe Cup Apio project file.

[env:default]

; Board id.

board = ice40-up5k

; Top module name (top.sv)

top-module = top

El archivo de las definiciones de los pins es llamado pinout.pcf,

# DigiKey Cofffe Cup Apio pins definitions file

set_io LED_R 41

set_io LED_G 40

set_io LED_B 39

set_io SW[0] 23

set_io SW[1] 25

set_io SW[2] 34

set_io SW[3] 43

set_io clk 35

El APIO lint es usado para verificar errores,

Digikey_Coffee_Cup # apio lint

Ahora se procede a contruir el projecto,

Digikey_Coffee_Cup # apio build

El sistema APIO provee una reporte de los recursos usados en el FPGA así,

Digikey_Coffee_Cup # apio report

Esto genera un reporte de los recursos utilizados,

Using env default (ice40-up5k)

Setting shell vars.

----------------------------------------------------------------------------------------------------------------------------------------

Formatting pnr report.

FPGA Resource Utilization

┌──────────────────┬────────┬──────────┬─────────┐

│ RESOURCE │ USED │ TOTAL │ UTIL. │

├──────────────────┼────────┼──────────┼─────────┤

│ ICESTORM_DSP │ │ 8 │ │

│ ICESTORM_HFOSC │ │ 1 │ │

│ ICESTORM_LC │ 32 │ 5280 │ 0% │

│ ICESTORM_LFOSC │ │ 1 │ │

│ ICESTORM_PLL │ │ 1 │ │

│ ICESTORM_RAM │ │ 30 │ │

│ ICESTORM_SPRAM │ │ 4 │ │

│ IO_I3C │ │ 2 │ │

│ SB_GB │ 2 │ 8 │ 25% │

│ SB_I2C │ │ 2 │ │

│ SB_IO │ 8 │ 96 │ 8% │

│ SB_LEDDA_IP │ │ 1 │ │

│ SB_RGBA_DRV │ │ 1 │ │

│ SB_SPI │ │ 2 │ │

│ SB_WARMBOOT │ │ 1 │ │

└──────────────────┴────────┴──────────┴─────────┘

Clock Information

┌────────────────┬───────────────────┐

│ CLOCK │ MAX SPEED [Mhz] │

├────────────────┼───────────────────┤

│ clk │ 79.74 │

├────────────────┼───────────────────┤

│ counter[23]_ │ 232.23 │

└────────────────┴───────────────────┘

Run 'apio report --verbose' for more details.

===================================================== [SUCCESS] Took 0.22 seconds ======================================================

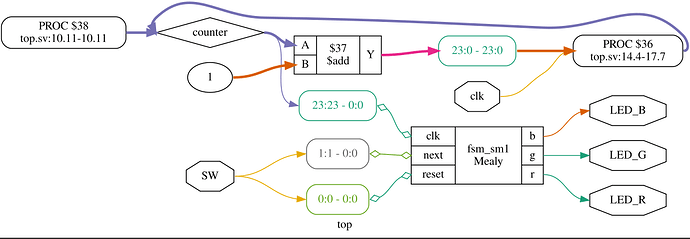

Para ver la gráfica visual de la configuracin de este demo se usa el siguiente comando,

Digikey_Coffee_Cup # apio graph

Esto genera un archivo .svg file que contiene una configuracin gráfica,

Asegurese de que los “jumpers” colocados apropiadamente en la plataforma Lattice ICE40 FPGA UltraPlus Breakout Board para programar el FLASH (Ver previo artículo). Una vez completado, se procede a subir la configuración del FPGA como sigue,

Digikey_Coffee_Cup # apio upload

El siguiente video muestra el Mealy FSM en el Lattice ICE40 FPGA UltraPlus Breakout Board,

Esto completa la descripción de la utilización de la herramienta APIO para la implementación de una máquina de estados finitos Mealy en SystemVerilog HDL para el Lattice ICE40 UltraPlus Breakout Board FPGA development kit. El Lattice FPGA ICE40 UltraPlus Breakout Board una excellente, económica , con un area de prototipo, que se puede usar para muchas aplicaciones y está disponible en DigiKey.

Que tenga un buen día.

Este artículo está disponible em inglés aquí.

This article is available in english here