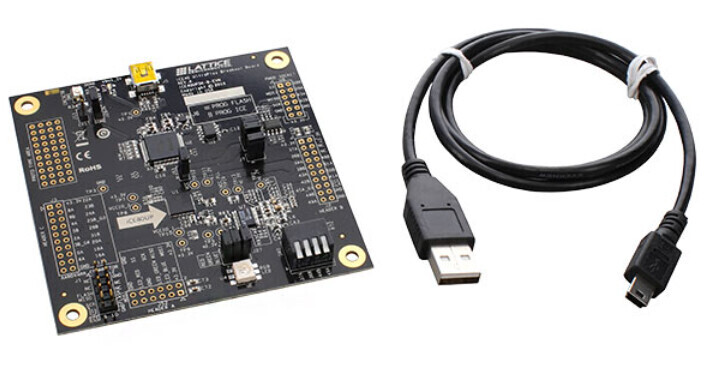

The present article outlines a simple Moore Finite State Machine (FSM) using the APIO mechanism for the Lattice ICE40 FPGA UltraPlus Breakout Board. Please refer to the previous article that outlines the installation of the APIO tool. The Lattice ICE40 FPGA UltraPlus Breakout Board is great development board,

A Moore Finite State Machine (FSM) example using the APIO mechanism will be implemented using SystemVerilog HDL for this platform. The APIO system already supports SystemVerilog HDL. The Moore Finite State Machine (FSM) diagram for this example is shown below,

The generic Moore FSM block diagram applicable to this demo is shown below,

The state diagram illustrate the Moore FSM state definitions, the relevant state transitions based on the state of the input next input to the system. This discrete next input is connected to a switch in the board that will be used to stop the transition process at any time taking place in the FPGA. The 12 MHz clock will be divided with an auxiliary divider to make these transitions visible to the human eye on the platform. The Moore FSM outputs are r, g, b, which will be connected to the RGB LED in the Lattice ICE40 FPGA UltraPlus Breakout Board for this demo. Each state represents the RED, BLUE and GREEN colors in that particular order and it will loop over and over again each second, unless the next discrete control input is deactivated. In that situation that transitions will stop and the FPGA Moore FSM will remain in that particular state. A provision for asynchronous reset is provided in the system for RED to be the reset state.. The following relevant files were used in this demo, the first one is the SystemVerilog HDL top.sv system,

//Digikey Coffee Cup SystemVerilog HDL Moore State Machine

module top(input [3:0] SW, input clk, output LED_R, output LED_G, output LED_B);

Moore fsm_sm1(.clk(counter[23]),.reset(SW[0]), .next(SW[1]), .r(LED_R), .g(LED_G), .b(LED_B));

//Auxiliary counter to divide the clock to be used in the Moore State Machine Demo

reg [23:0] counter;

initial begin

counter = 0;

end

always_ff @(posedge clk)

begin

counter <= counter + 1;

end

endmodule

The SystemVerilog HDL for the Moore State Machine is called moore_fsm.sv,

//Digikey Coffee Cup SystemVerilog HDL Moore State Machine

module Moore(

input logic clk,

input logic reset,

input logic next,

output logic r, g, b

);

typedef enum logic [1:0] {RED, BLUE, GREEN} statetype;

statetype state, nextstate;

// state register

always_ff @(posedge clk, posedge reset)

if (reset)

state <= RED;

else

state <= nextstate;

// next state logic

always_comb

case (state)

RED: if (next) nextstate = BLUE;

else nextstate = RED;

BLUE: if (next) nextstate = GREEN;

else nextstate = BLUE;

GREEN: if (next) nextstate = RED;

else nextstate = GREEN;

default: nextstate = RED;

endcase

// output logic

assign r = ~(state == RED & state != GREEN & state != BLUE);

assign b = ~(state != RED & state != GREEN & state == BLUE);

assign g = ~(state != RED & state == GREEN & state != BLUE);

endmodule

All the SystemVerilog HDL and APIO project definition files in the project folder are shown below,

├── apio.ini

├── moore_fsm.sv

├── pinout.pcf

└── top.sv

The apio.ini is the file that defines the project as follows,

; DigiKey Cofffe Cup Apio project file.

[env:default]

; Board id.

board = ice40-up5k

; Top module name (top.sv)

top-module = top

The pinout.pcf pins definitions file is as follows,

# DigiKey Cofffe Cup Apio pins definitions file

set_io LED_R 41

set_io LED_G 40

set_io LED_B 39

set_io SW[0] 23

set_io SW[1] 25

set_io SW[2] 34

set_io SW[3] 43

set_io clk 35

The APIO lint is called to perform error checking,

Digikey_Coffee_Cup # apio lint

Then proceed to build it,

Digikey_Coffee_Cup # apio build

APIO provides a list of the total resources used using this command,

Digikey_Coffee_Cup # apio report

it will display this report the FPGA resource usage,

FPGA Resource Utilization

┌──────────────────┬────────┬──────────┬─────────┐

│ RESOURCE │ USED │ TOTAL │ UTIL. │

├──────────────────┼────────┼──────────┼─────────┤

│ ICESTORM_DSP │ │ 8 │ │

│ ICESTORM_HFOSC │ │ 1 │ │

│ ICESTORM_LC │ 32 │ 5280 │ 0% │

│ ICESTORM_LFOSC │ │ 1 │ │

│ ICESTORM_PLL │ │ 1 │ │

│ ICESTORM_RAM │ │ 30 │ │

│ ICESTORM_SPRAM │ │ 4 │ │

│ IO_I3C │ │ 2 │ │

│ SB_GB │ 2 │ 8 │ 25% │

│ SB_I2C │ │ 2 │ │

│ SB_IO │ 8 │ 96 │ 8% │

│ SB_LEDDA_IP │ │ 1 │ │

│ SB_RGBA_DRV │ │ 1 │ │

│ SB_SPI │ │ 2 │ │

│ SB_WARMBOOT │ │ 1 │ │

└──────────────────┴────────┴──────────┴─────────┘

Clock Information

┌────────────────┬───────────────────┐

│ CLOCK │ MAX SPEED [Mhz] │

├────────────────┼───────────────────┤

│ clk │ 79.74 │

├────────────────┼───────────────────┤

│ counter[23]_ │ 232.23 │

└────────────────┴───────────────────┘

Run 'apio report --verbose' for more details.

========================= [SUCCESS] Took 0.81 seconds ==========================

To see a visual graph of the configuration for this demo use the following command,

Digikey_Coffee_Cup # apio graph

This will generate an .svg file that contains the visual graph of the FPGA configuration shown in the next figure,

At this point, make sure that the jumpers in the Lattice ICE40 FPGA UltraPlus Breakout Board are connected to program the FLASH (See previous post). Once this is complete, then proceed to upload the configuration of the FPGA as follows,

Digikey_Coffee_Cup # apio upload

The following low resolution video shows the Moore FSM state transitions of RED, BLUE and GREEN, and by pressing the switch that is connected to next it stops the FSM in that state until it is released, then it continues looping over.

This completes this overview of using the APIO for the implementation of a Moore Finite State Machine in SystemVerilog HDL for the Lattice ICE40 UltraPlus Breakout Board FPGA development kit. The Lattice FPGA ICE40 UltraPlus Breakout Board is an excellent, inexpensive, with a prototype area FPGA development board that can be used for many applications and is available at DigiKey.

Have a great day!

Este artículo está disponible en español aquí

This article is available in spanish here.