程式碼下載

spi_3_wire_master.vhd (9.1 KB)

特點

- 序列週邊介面(Serial Peripheral Interface ,簡稱 SPI)3 線主元件的 VHDL 原始碼

- 可配置的從屬數量

- 可配置的命令寬度

- 可配置的資料寬度

- 可選的極性和相位

- 可選的速度

介紹

本文詳細介紹了一個用於 CPLD 和 FPGA 的 SPI 3 線主控元件,該元件採用 VHDL 語言編寫。此組件使用 Quartus II 12.1 版設計。資源需求取決於具體實現(即所需的從屬數量和資料寬度)。圖 1 展示了一個整合到系統中的 SPI 3 線主控的典型範例。

圖 1. 範例應用

背景

SPI 3 線通訊方案是一種半雙工資料連結。主控透過將從屬選擇(SS)線拉低來發起傳輸。由主控驅動的串列時脈(SCLK)線提供同步時脈來源。串列資料輸入/輸出線是一條雙向資料線,主控透過它傳送和接收資料。在典型情況下,主控會透過 SDIO 線發送指定長度的命令。如果是寫入指令,主控隨後會在線上發送固定長度的資料。如果是讀取指令,從屬發送數據,主控接收固定長度的數據回應。

一個主控可以透過多種技術與多個從屬通訊。在最常見的配置中,每個從屬都有一條獨立的 SS 線,但與其他從屬共用 SCLK 和 SDIO 線。當每個從屬的 SS 線未被拉低時,它們會忽略共用線路。此拓樸如上圖 1 所示。

SPI 有四種工作模式,基於兩個參數:時脈極性(CPOL)和時脈相位(CPHA)。主控和從屬必須使用相同的模式才能清楚地通訊。如果 CPOL 為零,則 SCLK 通常為低電平,第一個時脈沿為上升沿。如果 CPOL 為 1,則 SCLK 通常為高電平,第一個時脈沿為下降沿。CPHA 定義資料對齊。如果 CPHA 為零,則第一個資料位元在 SS 下降沿寫入,並在第一個 SCLK 沿讀取。如果 CPHA 為 1,則資料在第一個 SCLK 沿寫入,並在第二個 SCLK 沿讀取。圖 2 中的時序圖描述了四種 SPI 模式。

圖 2. SPI 3 線時序圖

連接埠描述

表 1 描述了 SPI 主控的連接埠。從屬的數量由 GENERIC 參數 slaves 在 ENTITY 中聲明。命令匯流排寬度由 GENERIC 參數 cmd_width 聲明。發送和接收資料匯流排寬度由 GENERIC 參數 d_width 聲明。

表 1. 連接埠描述

時脈

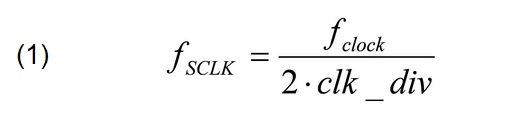

clock 和 clk_div 輸入定義 SCLK 的頻率(即 SPI 資料速率)。clock 是用來操作元件內部同步邏輯的系統時脈。clk_div 整數輸入允許使用者設定目前傳輸發生的相對速度。clk_div 是 SCLK 轉接之間的 clock 週期數,如公式 1 所示。

當 clk_div 連接埠設定為 1 時,SCLK 頻率為 clock 頻率的一半,並設定為可實現的最大資料速率。enable 引腳會將 clk_div 的值閂鎖到元件中以啟動每個傳輸,因此可以調整各個從屬的資料速率。

將 clk_div 連接埠設定為恆定值可永久設定資料速率。如果 clk_div 設定為 0,則元件會將其設為 1。因此,將 clk_div 連接埠設定為低電平可使元件始終以最大速度運作。

極性和相位

enable 引腳在每次傳輸開始時閂鎖 cpol 和 cpha 的標準邏輯值。這允許使用獨立的 SPI 模式與各個從設備進行通訊。如果所有從屬都需要相同的模式,則只需將 cpol 和 cpha 綁定到相應的邏輯電平即可。

命令和資料寬度

ENTITY 中的 cmd_width GENERIC 參數指定傳輸指令部分的長度。同樣,d_width GENERIC 參數指定傳輸資料部分的長度。圖 3 和圖 4 分別顯示了 CPOL = 0 和 CPHA = 0 時寫入和讀取傳輸的訊號時序圖。在這些時序圖中,K = cmd_width,M = d_width。如圖所示,命令和資料均按 MSB 優先發送。

圖 3. 寫入傳輸的時序圖(CPOL = 0、CPHA = 0)

圖 4. 讀取傳輸的時序圖(CPOL = 0,CPHA = 0)

傳輸

busy 輸出埠上的低邏輯電平表示元件已準備好接受指令。元件在 enable 輸入被宣告的第一個 clock 上升沿閂鎖傳輸的設定、位址、讀寫、指令和資料。在接下來的 clock 上,元件宣告 busy 訊號並開始執行傳輸。完成後,如果傳輸是讀取,元件會在 rx_data 連接埠輸出接收到的資料。該資料將保留在連接埠上,直到元件從後續讀取傳輸接收到新資料。元件將 busy 設定為低電平,以通知使用者傳輸已完成且接收資料可用。然後,元件立即準備好執行下一條指令。

圖 3 顯示了典型傳輸的時序圖。此 SPI 3 線主控被配置為一個從屬,指令寬度為 8-bit,資料寬度為 8-bit。enable 脈衝閂鎖的設定如下:CPOL = 1、CPHA = 1、clk_div = 0(最大速度為 fsclk = fclock/2)、從屬位址為 0、rw = 0(表示讀取傳輸)以及指令「10011001」。由於這是一個讀取傳輸,因此 tx_data 連接埠無關緊要。然後,SPI 3 線主控發送命令並接收從屬的回應。傳輸完成後,它將 busy 輸出設為低電平,並在 rx_data 連接埠上置位接收到的資料「01010101」。

圖 5. 典型傳輸的時序圖

重置

reset_n 輸入連接埠必須為邏輯高電平,SPI 3 線主組件才能運作。此連接埠上的低電平訊號會非同步重置組件。重置期間,元件保持 busy 連接埠和所有 ss_n 輸出為高電位。sdio 連接埠處於高阻態,rx_data 輸出埠清零。重置結束後,busy 連接埠會在下一個時脈週期置低,指示 SPI 主控已準備好進行通訊。

總結

SPI 3 線主控是一種靈活的可編程邏輯元件,可透過單一平行介面與各種從屬進行通訊。它允許與用戶指定數量的從屬進行通訊,這些從屬可能需要獨立的 SPI 模式和串行時脈速度。它還允許用戶配置所需的命令和資料大小。

相關主題

SPI 主控(VHDL) - 這是一個 4 線 SPI 主控元件。

SPI 從屬(VHDL) - 這是一個 4 線 SPI 從屬元件。