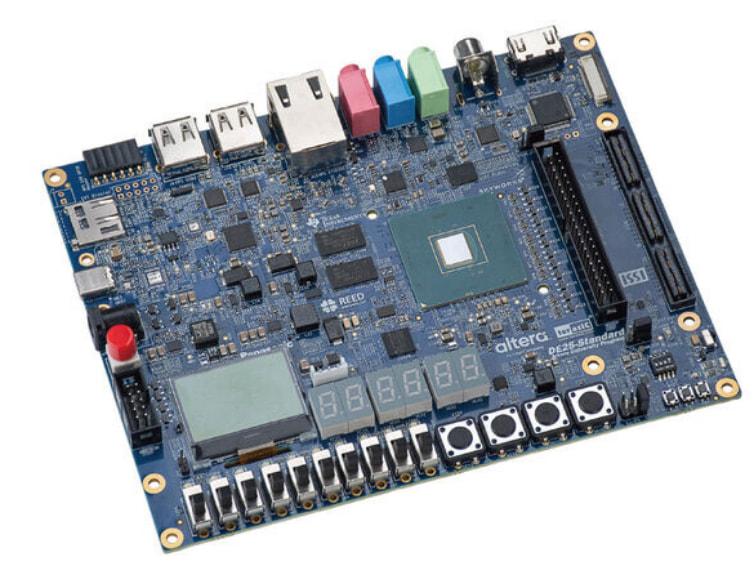

El propósito de este artículo es describir como programar la memoria Quad Serial Peripheral Interface (QSPI) NOR flash no-volatil en la plataforma DE-25 FPGA Dev Kit.

En el modo Quad-SPI hay 6 terminales que son usados: 4 son para data (para aumentar la metrica de velocidad de transferencia) y 2 adicionales, uno para el reloj y la otra linea para seleccionar el artefacto como se muestra a continuación,

Para programar el QSPI en este caso estaremos usando el formato del archivo conocido como JTAG Indirect Configuration File (.jic).

La plataforma DE-25 FPGA Dev Kit provee los siguientes dos modos de configuración:

- Programación JTAG: del estándar IEEE, JTAG es denominado Joint Test Action Group, en este modo, el archivo binario es transferido directamente a el Agilex 5 FPGA. El FPGA en este modo, retiene la configuración hasta que se le desconecte la energía eléctrica y la misma se pierde.

- AS program: Modo de programación conocido como Active Serial programming, el archivo binario se transfiere a la memoria de configuración QSPI. El QSPI es una memoria no-volátil, el código que define el sistema se retiene aún cuando se le desconecte la energía eléctrica suplida a la plataforma DE-25 FPGA Dev Kit. Cuando se le conecte la energía, la configuración que está almacenada en la memoria QSPI es automáticamente transferida a el Agilex 5 FPGA.

Para programar la memoria QSPI non-volátil, por favot configure los siguientes switches para poner la plataforma en modo de programación Active Serial (AS),

Asumiendo que el DE-25 FPGA Dev Kit está encendido, y el cable está conectado a la computadora, y el archivo SRAM Object File (.sof) en esta caso top.sof ya ha sido generado apropiadamente, primero se procede a usar el siguiente comando en el directorio donde el archivo top.sof file reside y se convertira al siguente denominado top.jic,

digikey_coffee_cup $: quartus_pfg -c top.sof top.jic -o device=MT25QU128 -o flash_lo

Este proceso produce el archivo top.jic que se utiliza en el próximo paso de programación. Ahora guarde el siguiente archivo conocido como el Chain Description File called flash.cdf en el directorio en consideración,

JedecChain;

FileRevision(JESD32A);

DefaultMfr(6E);

P ActionCode(Cfg)

Device PartName(A5ED013BB32AE4SCS) Path("./") File("top.jic") MfrSpec(OpMask(1) SEC_Device(MT25QU128) Child_OpMask(1 1));

ChainEnd;

AlteraBegin;

ChainType(JTAG);

Frequency(16000000);

AlteraEnd;

Este archivo conocido como el Chain Description File en inglés, especifica entre otras cosas, el número de parte relevante (del FPGA) en este caso A5ED013BB32AE4SCS y el artefacto de memoria QSPI MT25QU128 y la frecuencia del reloj JTAG a 16 MHz. Final, mentem, se programa la memoria QSPI no-volátil como se muestra a continuación,

digikey_coffee_cup $: quartus_pgm -m jtag -c 1 ./flash.cdf

Se apaga la plataforma DE-25 FPGA Dev Kit nuevamente para verificar que el diseño está implementando el diseño en el FPGA. El FPGA deberia de implentar el sistema que se desea via QSPI despues del proceso de encender la plataforma. Esto ha completado la descripción de la conversión del top.sof a el top.jic y como transferirlo a la memoria no-volátil QSPI device en el modo de programación Active Serial (AS).

El DE-25 FPGA Dev Kit es una plataforma poderosa HPS/FPGA con el Agilex 5 (disponible en la serie D y la serie E-Series dependiendo del caso en cosideración) capaz de implementar módulos Tensor AI,

que van mas allá que los tradicionales/clásicos módulos de DSP del pasado,

y está disponible en DigiKey.

Que tenga un buen día.

Este artículo está disponible en inglés aquí.

This article is available in english here.