APDahlen Applications Engineer

はじめに

この投稿では、Microchipの PIC16 構成可能ロジックブロック(CLB:Configurable Logic Block)ペリフェラルを紹介します。ダウンロード可能なSeed Projectも含まれており、すぐに始められます。このSeed Projectは、ブレッドボードの構築に集中できるように、動作するプログラムシェルを提供することを意図しています。このSeed Projectは、ステッピングモータドライバ(近日公開予定)のような大規模なプログラムの基礎を形成することができます。

Seed Projectには小さなVerilogサンプルが含まれています。Verilogの最も重要な点はCLKソースの選択で、Verilogの強力なalways @(posedge CLK)ステートメントを使用できます。

Seed ProjectはSeedProject.X.zip(541.2 KB)からダウンロードできます。

![]() おおよその読了時間:5分

おおよその読了時間:5分

MicrochipのPIC構成可能ロジックブロックとは何でしょうか?

Microchipの最新の PIC16 マイクロコントローラには、構成可能ロジックブロック(CLB)が搭載されています。これは複合プログラマブルロジックデバイス(CPLD)や極小規模のフィールドプログラマブルゲートアレイ(FPGA)が提供するグルーロジックのような役割を果たします。

-

デジタルロジックは、強化された PIC16 と同じ半導体チップ上に搭載されています。

-

PICマイクコントローラから独立して動作させることもできます。

-

PICと同じクロックドメインで動作するようにプログラムすることもできます。例えば、各ブロックには選択可能なクロックソースを備えた同期ロジックが搭載されています。CLB入力は、メインのマイクロコントローラの高周波発振器やタイマオーバーフローなどの他の信号に同期させることができます。

-

CLBピンは物理的なI/Oピンに接続することができます。

-

入力ピンの弱プルアップ抵抗や、一部のPIC出力周辺レジスタは引き続き動作します。

Seed Projectの説明

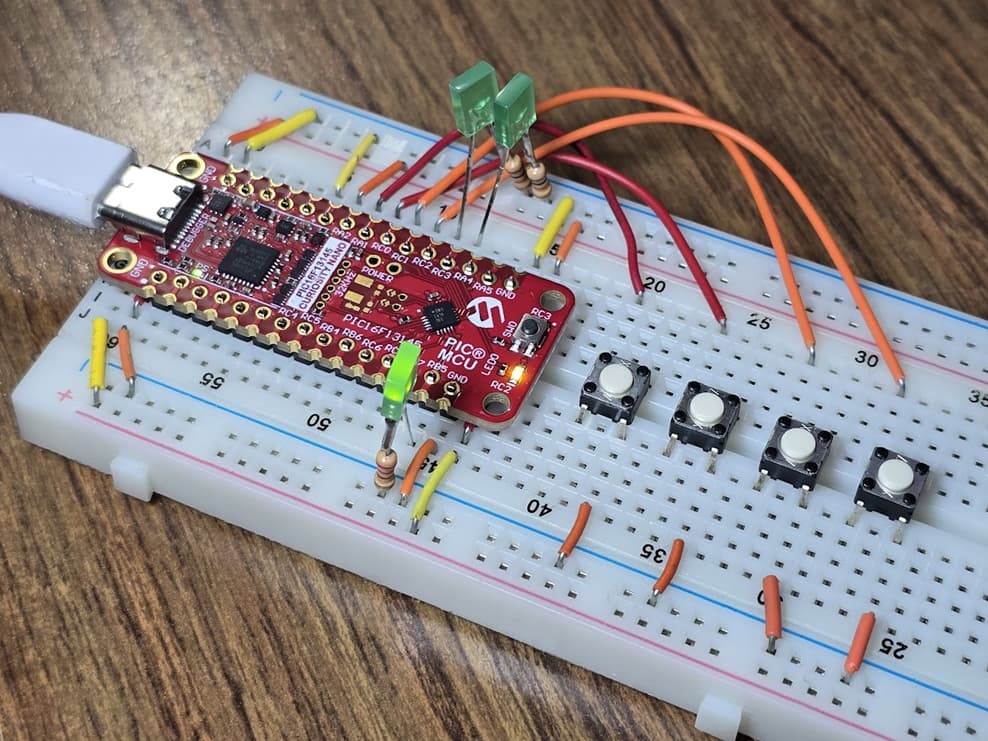

このエンジニアリング概要では、単独の論理素子としてのCLBにほぼ特化しています。このプロジェクトでは、図1に示すMicrochipの PIC16F13145 curiosity 評価ボードを中心に展開します。

ここでは、CLBを4入力8出力のロジックブロックとして定義します。PIC16 マイクロコントローラのコアは控えめに使用します。実際には、main()は空のループであり、1つのISRを使用して50%デューティサイクルのパルス/秒信号を提供し、RB5出力ピンに出力します。この物理信号は、ステートマシンの設計とデバッグに役立つ可能性があります。

図1: 筆者の作業台に設置されたMicrochipの PIC16F13145 のブレッドボードの画像

CLBのSeed Projectの配線とピンの割り当て

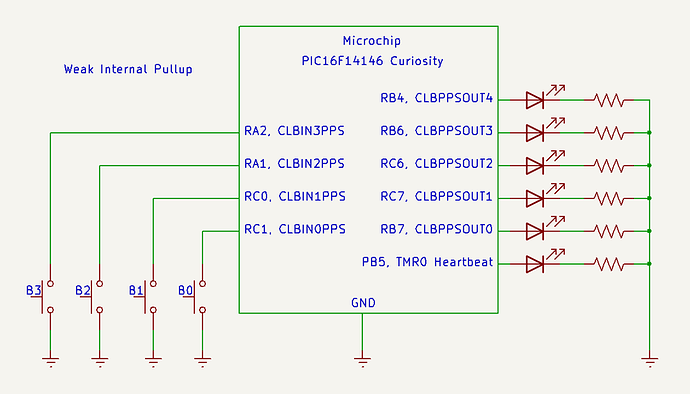

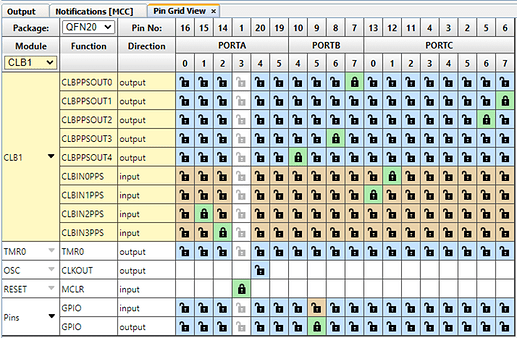

ブレッドボード回路の回路図を図2に、MPLAB のピン配置を図3と図4に示します。これは、入力信号と出力信号の連続したピン割り当てでブレッドボードに適した設計になっています。

プロジェクトの特長は以下のとおりです。

-

図2に示すように4つの押ボタンがあります。

-

CLBのピン配置は図3のとおりです。

-

入力はCLBINxPPSとして識別されます。

-

出力はCLBPPSOUTxとして識別されます。

-

-

図4に示すように、入力ピンに弱プルアップ抵抗を使用することで、必要な部品点数を最小限に抑えています。

-

出力ピンの状態を可視化するために6個のLEDを搭載しています。簡単にするために、図1(緑色の四角いLED)のように抵抗をはんだ付けしたLEDを使用しています。この使いやすいロジックLEDプローブの詳細については、こちらのリンクをご参照ください。

図2: 押ボタンとLEDを備えた PIC16F13145-curiosity ブレッドボード回路の回路図

図3: SeedプロジェクトのI/Oピンの構成

技術的なヒント: 図3のピン配置はランダムに見えるかもしれません。しかし、これらはcuriosity評価ボードのレイアウトを考慮して便宜的に選択されたものです。例えば、出力ピンRB7、RC7、RC6、RB6、およびRB4は連続した順序です。同様に、入力RA2、RA1、RC0、およびRC1は、図1の押ボタンの配線のインターフェースに示されているように、連続した順序になっています。

図4: 弱プルアップ抵抗の有効を示すテーブル表示

Seed Projectの属性

Seed Projectのロジックを図5に示します。このプロジェクトはブレッドボード製作を支援するために設計されています。そのため、ロジックは非常にシンプルです。

-

各入力は出力ピンに直接ルーティングされています。例えばCLBIN3PPS はPPS_OUT3 にルーティングされています。

-

各入力はアクティブローからアクティブハイに論理を反転させるインバータが挿入されています。各入力ピンは弱プルアップ抵抗にプログラムされています。押ボタンは、押されるとこの抵抗をプルダウンします(負論理)。

-

小さなVerilogのサンプルがCLK_Demoとして用意されています。

図 5: ゲートレベルと階層型 Verilogモジュールを含むSeed Projectの混合CLBロジック

Verilogデモの説明

Verilogデモコードはリスト1です。このコードは、CLKパルスの立ち上がりエッジで遷移する単純な1/2分周回路として記述されています。モジュールの中心部分では、q <= !q;という代入文が見られます。

CLK信号は、このVerilogコードの最も重要な要素の1つです。 この隠された信号は、Verilogの強力なalways @(posedge CLK)手続き的ブロックで使用できます。

module CLK_Demo (CLK, enable, q);

input CLK;

input enable;

output reg q;

always @(posedge CLK) begin

if (enable) begin

q <= !q;

end

end

endmodule

リスト1: Seed Projectで使用されているVerilogコード

図5に示すように、イネーブル信号はCLBIN0PPSで駆動されます。Verilog駆動のLED点滅は、B0押ボタンが押されたときにのみ発生します。

CLK信号の選択

CLK信号は、高周波発振器から タイマオーバーフローまで、さまざまなマイクロコントローラ信号から選択できます。Seed Projectでは、以前に設定した1msの タイマオーバーフロー信号を使用します。図6に示すように、RB4に接続されたLEDを点滅させるための低速信号を供給するために、これは更に1/128に分周されます。

図 6: CLBのCLK信号の構成

回路構成

このSeed Projectは、PIC16F13145 でMicrochipのCLBをすぐに使い始められるように設計されています。図2を参考にしてブレッドボード上に回路を構築します。その後、MPLAB を使用してSeed Projectをロードできます。その後、必要に応じてトラブルシューティングを開始できます。

技術的なヒント: 弱プルアップ抵抗で構成されたマイクロコントローラにはレール電圧が存在します。これは電圧計で検出でき、押ボタンが回路に正しく配線されていることを確認できます。

MicrochipのCLBの次のステップ

Seed Projectが実行されると、独自の論理回路のプログラミングを開始できます。4つの入力信号と8つの出力信号を持つCLBは、単一ゲート、積和回路、さらにはステートマシンに至るまで、多くの典型的なデジタル回路を検討するために使用することができます。デモとして、イネーブル入力と回転方向入力を持つハーフステップのステップモータ駆動回路を作りました。近いうちにその設計を投稿します。

ご健闘をお祈りします。

APDahlen

著者による関連記事

この記事が気に入った場合は、以下の関連記事も役立つかもしれません。

-

従来の555タイマを形成することによる、類似のPIC構成可能ロジックセル(CLC)の紹介: Getting Started with Microchip’s Configurable Logic Cells (CLC): Turn Your PIC16 into a 555 Timer

-

MCC MelodyをPIC16プロジェクトに統合するための最適なコーディング手法: Preventing Microchip’s MCC Melody from Overwriting Your Code

-

PIC16マイクロコントローラを搭載したライトカーテンの分解: Light Curtain Teardown; Inside the Banner EZ-Screen LP

-

PIC、AVR、8051を中心に、教室に最適なマイクロコントローラを特定:教育:教室で使用するマイクロコントローラの選択

著者について

Aaron Dahlen氏、LCDR USCG(退役)は、DigiKeyでアプリケーションエンジニアを務めています。彼は、技術者およびエンジニアとしての27年間の軍役を通じて構築されたユニークなエレクトロニクスおよびオートメーションのベースを持っており、これは12年間教壇に立ったことによってさらに強化されました(経験と知識の融合)。ミネソタ州立大学Mankato校でMSEEの学位を取得したDahlen氏は、ABET認定EEプログラムで教鞭をとり、EETプログラムのプログラムコーディネーターを務め、軍の電子技術者にコンポーネントレベルの修理を教えてきました。

Dahlen氏は、ミネソタ州北部の故郷に戻り、コンデンサ探しから始まった数十年にわたる旅を終えました。こちらをお読みください。