セラミックコンデンサ

セラミックコンデンサは、チタン酸バリウム(BaTiO3)を主成分とする各種セラミック誘電体材料を使用した静電デバイスです。無極性で、量と質のスペクトル(quantity-quality spectrum)の多くの範囲をカバーする特性を持っていますが、やや質に偏っているのかもしれません。セラミックコンデンサは、用途に応じて構造や誘電体特性のバリエーションが豊富で、この広い応用性とともに比較的安価な構造であることから、販売個数ベースで、現在最も普及しているコンデンサです。

デバイスの構造

初期のデバイスは、2つの金属電極の間に単層のセラミック誘電体(通常、円形)を挟んだ構造になっていました。金属電極にリード線を取り付け、その組み立て品をセラミックやエポキシなどの絶縁材料で封止しています。この構造は、ACラインや高電圧用途のデバイスではまだ見られるものの、この構造を採用したデバイスで面実装に適したものはほとんどなく、多くのアプリケーションでその魅力が限定されています。

現在では、電極と誘電体材料を交互に薄く積層し、小さなパッケージ容積に大きな電極面積を実現した積層セラミックチップコンデンサ(MLCC)が主流となっています。このようなデバイスは、未焼成のセラミック「粘土」の薄いシートを押し出し、その上に、スクリーン印刷と同様のプロセスによって、細かく分割された形の電極材料が堆積されることにより構成されます。この「シート」を何枚か重ねて圧縮し、希望する数の電極層を作り、個々のコンデンサの形にカットし、高温のオーブンで焼成してセラミック誘電体材料を硬化させ、電極金属中の粒子を融着させます。その後、端子を形成し、最終検査に合格したデバイスは梱包して出荷されます。

上図:MLCCの簡略化された製造工程(出典:WikiMedia Commons)

使用可能な容量と電圧の範囲

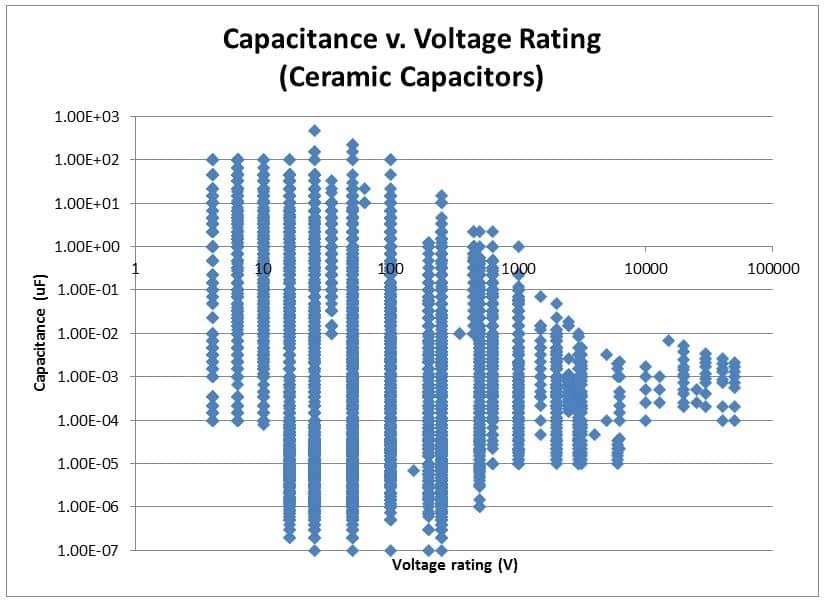

以下のチャートは、執筆時点でDigi-Keyから入手可能なセラミックコンデンサの電圧と静電容量の組み合わせの範囲を示しています。なお、グラフは両軸とも対数になっています。

アプリケーションにおける長所と短所

セラミックコンデンサ(特にMLCC)は、汎用性、経済性、耐久性に優れ、電気特性も良好であることから、広く普及しています。適用領域が重複する場合、セラミックコンデンサは一般に、バルク電力処理に使用される他のタイプ(アルミニウム、タンタルなど)に比べて良好な特性を持ちますが、最高の安定性または精度が必要な場合に使用される薄膜や他のタイプに比べてやや特性が劣ります。

セラミックコンデンサの汎用性は、上図のように静電容量で約9桁、電圧で約4桁という利用できる数値の幅にも表れており、これほど幅広いスケールを持つ技術はそう多くはありません。セラミックコンデンサの原材料は、特別高価なものではなく、効率的に利用できるものが多く、高い精度と工程管理が要求されるものの、基本的な製造工程はそれほど複雑なものではありません。このような特性により、MLCCは毎年何十億個と生産され、しばしば1円以下の単価で提供されます。アプリケーションの観点からは、これらは長寿命のアプリケーションに最適です。 本質的に耐久性のある材料(金属およびセラミック)のレイヤーケーキであるため、強力な摩耗メカニズム、温度、圧力、または電圧の反転に対する深刻な脆弱性、電解デバイスに見られる漏れ、燃焼、または毒性のリスクがありません。電解デバイスのように比較的抵抗の高い電解液に依存しないため、セラミックコンデンサのESRは非常に低く、その内部形状(およびMLCCの場合は短い端子長さ)から、多くの場合、基板レイアウトがESRの主因となります。

セラミックコンデンサのアプリケーション上の弱点としては、機械的な脆弱性、自己修復機能の欠如、高容量値でのコスト、およびセラミック誘電体材料の特定のフォーミュレーション(配合組成)に依存して環境および電気動作条件へのパラメータの依存度が異なることなどが挙げられます。

セラミックコンデンサは、他のセラミック製品同様、非常にもろく、柔軟性に欠けています。その結果、それらは機械的ストレスまたは熱衝撃に対し損傷しやすく、最終製品での組み立ておよびサービス中にそのような要因を注意深く軽減する必要があります。セラミックコンデンサは比較的不活性な「鉄と石」構造であるため、自己修復機構が存在しません。誘電体破壊によるストレスはデバイスに回復不可能な損傷を与える傾向があり、誘電体の弱い箇所を製造中に容易に「焼き切る」ことができないため、実質的な安全係数を高めるには、誘電体を厚くする必要があります。このため、セラミックコンデンサは電解タイプに比べて1ファラッドあたりのコストが高く、また、サイズが大きくなるほど機械的損傷のリスクが高まるため、数10マイクロファラッドを超える値のセラミックコンデンサの魅力や入手性は低くなっています。最後に、多くのセラミック誘電体のフォーミュレーションは、一般に誘電率に比例する程度に、パラメトリックに安定しておらず、温度や誘電体応力に対して線形でないことが挙げられます。そのため、大容量のセラミックコンデンサは、精密な用途には適さないことがよくあります。

設計上の重要な考慮事項

温度特性と誘電体の分類

多くのセラミック誘電体材料が一般に使用されていますが、材料によって、体積効率、温度依存性、損失特性および非理想的な挙動が大きく異なります。デバイスはその温度特性によって分類され、EIA(Electronics Industry Association、米国電子工業会)やIEC(International Electrotechnical Commission、国際電気標準会議)、米軍などの規格団体が長年にわたって確立したさまざまな線引きや識別の仕組みがあります。

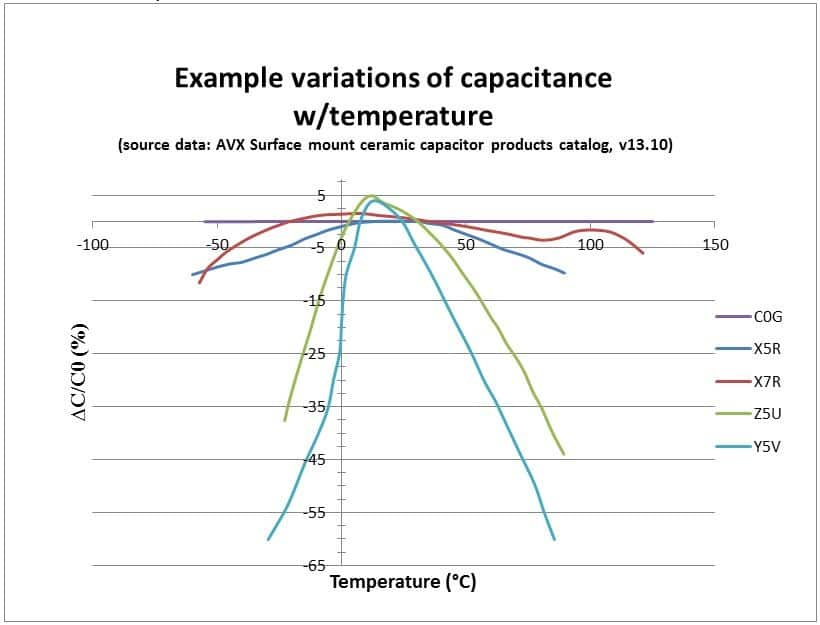

これらのシステムに共通するのは、静電容量の質と量の違いであり、精密アナログ回路や共振回路アプリケーションに用いられる低損失/高安定/温度線形タイプと、安定性や直線性は劣るが体積あたりの静電容量が大きいタイプは、異なる使い方をされています。IEC規格では、静電容量の質と量に着目して設計された誘電体を、それぞれクラス1、クラス2と定めています。EIA規格では、IEC規格と同様に、品質重視の誘電体をクラスI(クラスの数字は、必ずしもローマ数字に限定はしていない)としていますが、IECクラス2のデバイスをEIAクラスIIとIIIに細分化しています。EIAクラスIIは、温度に対するパラメータの安定性(通常-50°Cから85°C以上の範囲で±15%以下)に品質を保持するもので、EIAクラスIIIは、体積効率を追求するために温度安定性を追求せず、狭い温度範囲でのパラメータの変動幅が大きい誘電体です。+10°~+85°Cで+22%/-56%、-30°~+85°Cで+22%/-82%は一般的なクラスIIIの制限値です。下図は、あるメーカーの誘電体の温度特性を数種類に分けて、その現象をグラフ化したものです。

さまざまな誘電体のフォーミュレーションが、それぞれ一般的な誘電体クラスで利用可能です。クラス1の誘電体については静電容量の温度係数で分類され、その他のデバイスクラスについては指定された温度範囲での静電容量の変化に対する制限で分類されます。

いくつかの分類スキームの「Secret decoder rings(シークレットデコーダリング)」は、添付の表に示されています。IEC Class 1(EIA Class I)の誘電体を持つMLCCは、静電容量の温度係数を制御して設計されており、これらのデバイスの静電容量は温度に対して線形関数となります。EIAクラスIの誘電体分類は、その直線の傾きとその傾きの許容範囲を示すものです。これに対して、クラスIIとIIIのセラミックの誘電体分類は、次の2つの量で許容範囲を示します。1)温度の関数としての静電容量値の変化で、標準温度(通常25℃)での値に対する変化をパーセンテージで表示、2)その変化範囲が適用される温度範囲、です。その範囲内の温度特性の傾きについては何も暗示されておらず、ほとんどは直線的どころか単調ですらありません。

IEC class 2(EIA class II/III)の誘電体の分類について、2つの重要な注意事項があります。

-

これらは、温度による静電容量の変化のみを示しています。その他の影響はΔCの数値には含まれず、またこれらの影響は非常に大きい場合があります。(静電容量電圧係数の項参照)

-

この表は、誘電体組成を絶対的に規定するものではなく、温度特性だけでデバイスをグループ分けする手段です。同じ値、許容差、電圧定格、および誘電体分類であっても、異なる品番(特にパッケージサイズの異なる品番)は、アプリケーションよって異なる挙動を示すことがあります。

許容差仕様

セラミックコンデンサの製造許容差と温度特性の区別は、数値の大きさがよく似ていること、両者をパーセントで表すことが一般的であること、および用語が明確には定義されていないことなどから、誤解されやすいです。正確に言えば、セラミックコンデンサの「許容差」仕様は、製造上のばらつきの結果として、標準的な試験条件下でデバイスの値に許容されるばらつきを示します。通常許容差は、公称値に対するパーセンテージで規定され、標準化された試験条件下における、公称値に対する同一品番の異なるデバイス間のばらつきを指します。言い換えれば、製造ラインから出荷される部品の均一性の尺度です。

一方、セラミックコンデンサの「温度特性」はあるデバイスの静電容量が、そのデバイスが規定する動作温度範囲において、温度によってどの程度変化することが予想されるかを示しています。「温度係数」という用語は、温度依存性が多少とも線形であるクラスIの誘電体を使用したデバイスに用いるのが最も適切であり、「温度特性」という用語は、温度によって容量が明らかに非線形に変化するEIAクラスIIおよびIIIの誘電体を使用したコンデンサに用いるのがより適しています。

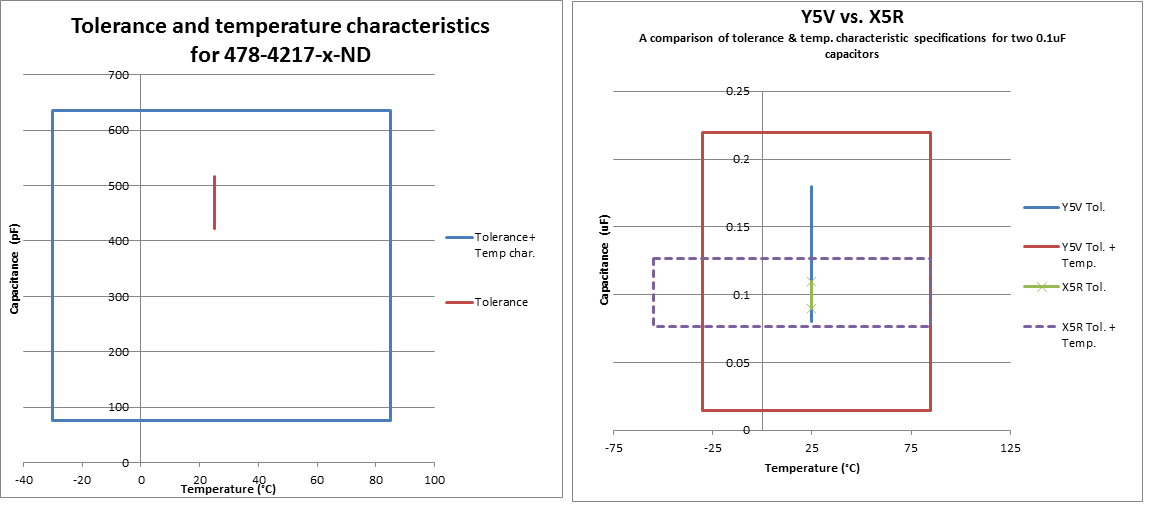

例えば、品番478-4217-1-NDは、公称470pFの静電容量、±10%の許容差、そしてY5Vの温度特性を持つセラミックディスクコンデンサです。指定された試験条件で測定した場合、この品番のデバイスは423pF~517pFの間の静電容量を示すはずです。これはデバイスの公差で、左下のグラフの赤い線上のどこかの点が、この品番のデバイスの静電容量を表しているということを述べています。しかし、Y5V温度特性は、-30°Cから+85°Cの温度範囲で測定した場合、標準試験条件での値に対してさらに+22%/-82%の容量変化があることを示しています。言い換えれば、デバイスは、静電容量対温度のプロット(指定の試験信号で測定、指定の温度履歴など)が、垂直方向に青いボックス内にとどまり、赤い線を通過する限り、仕様を満たすことができ、ボックスの水平(温度)限界の外側では、静電容量の値は保証されません...。温度特性を考慮すると、この(公称)470pFのコンデンサは、76~630pF(25°Cを除く)の静電容量を示していても、完全に規格内に収まっていることが分かります。さらに、経年変化や電圧の影響を変数として加えることで、デバイスの規定値に違反することなく、実際に観測される静電容量はさらに広範囲に変化することになります。ここでいう「許容差」と「温度特性」の区別は、かなり重要であることは明らかです。設計者が公称値の10%以内の値を示すと誤解している場合、アプリケーションが室温から大きく外れて使用される場合、失望することになります。

品番490-3271-2-NDと490-5920-2-NDを比較します。どちらもEIA 0402(1005メートル法)パッケージの0.1uF、25Vのコンデンサです。前者はY5V特性のクラスIII誘電体を使用し、許容差は-20%~+80%で、数量あたりの定価は執筆時点で0.00399ドルです。後者はX5R特性のクラスII誘電体を使用し、±10%の許容差があり、0.00483ドルで販売されています。温度特性を考慮した結果得られる許容差の範囲と温度特性を含めた全許容範囲を右上図にまとめています。前のチャートと同様に、温度の関数としての実際の静電容量がそれぞれのボックス内に留まり、25°Cの垂直線を通過する場合、組み立てラインから出荷されたデバイスは仕様通りと言えます。X5R(クラスII)はY5V(クラスIII)よりも3倍以上公称値に近く、より広い温度範囲でその状態を維持し、製造ばらつきと温度の複合効果によるデバイスの最大値と最小値の比率はクラスIIデバイスの方が10倍近く小さくなっています。1/10セント以下のコストで、必要な設計マージンの削減、生産歩留まりの向上、テスト要件の削減、製品寿命の向上などを実現することができるのです。そんな利点があれば、1セントだって惜しくないのに、1セントもかからないのです......。

静電容量の電圧係数

セラミックコンデンサは、直流バイアスレベルの変動により静電容量が変化します。つまり、 1Vp-p サイズの平均0Vの電圧でデバイスの静電容量を測定した場合は、10VのDCオフセットを持つ1Vの正弦波で同じデバイスをテストした場合とは異なる(通常はより大きい)値が得られることになります。この効果は、印加される電圧勾配の結果、誘電体の結晶構造にかかるストレスに起因し、その結果、誘電体の厚さ/デバイスの電圧定格に比例して大きくなります。他の条件が同じであれば(同じであることは稀ですが)、静電容量が同じように比例変化するためには、100VDCのデバイスは、25VDCのデバイスと比較して4倍のDCバイアスを必要とします。当然のことながら、その効果は誘電体のフォーミュレーションにも影響されます。EIAクラスIの誘電体は比較的小さな電圧係数を示し、DCバイアスをデバイスの定格電圧の0~100%の間で変化させたときに、観測される静電容量は通常最大でも数パーセント(多くはそれ以下)しか変化しません。EIAクラスII誘電体は、DCバイアスの影響を顕著に受け、20~60%の静電容量変化が当たり前になっています。このような変動は決して軽視できるものではありませんが、EIAクラスIII誘電体の静電容量が一般的に定格電圧で80~90%以上変動するのに比べれば、その変動は著しく小さいと言えます。いいえ、タイプミスではありません。EIAクラスIIIの誘電体材料を使用したセラミックコンデンサの実効容量は、DCバイアスによって単純に1桁変化することがあり ます。また、その効果は好ましくない非線形である場合もあります。一部のデバイスでは、定格DC電圧の20%までバイアスをかけると、静電容量が75%減少するものもあります。さらに悪いことに、この効果は温度の影響に累積されます(線形に加算されるわけではありませんが)。

さらに驚くべき(油断のならないの)は、DCバイアス効果の大きさとパッケージサイズとの関係です。より小さなパッケージに、より大きな容量を詰め込むには、どこかで妥協が必要です。その点は上の添付図に示され、同じメーカーの製品シリーズから3種類の1uF/16V/X5Rコンデンサについて、DCバイアスの関数として静電容量変化を示しています。主な違いはパッケージの大きさだけです。パッケージが小さくなったことの代償は明らかです。EIA0805(2012メートル法)パッケージのデバイス(緑)は5Vバイアスで数%の静電容量損失、よりアグレッシブな0402(1005メートル法)パッケージのデバイス(青)は同じ条件で70%近く損失し、0603(1608メートル法)パッケージのデバイス(赤)はその中間に位置していることがわかります。(データは、TDKのComponents Characteristic Viewer online toolより)多くのアプリケーションでは、DCバイアスと最小限の静電容量を維持することの両方が重要なので(例えば、低ドロップアウト電圧レギュレータの出力フィルタ)、そのことを知らなかった場合、不快な不利益を被る可能性は明らかです。しかし、これらの電圧依存効果に関する記述は、デバイスのデータシートに事実上記載されていないため、その存在を見落としたり、知らないままでいたりしやすく、異なる製品を比較する努力を複雑にしています。しかし、実際に存在することは間違いないので、デバイスを選択する際にはそのことを念頭に置いてください。

クラック

セラミック材料は脆く、比較的柔軟性に欠けるため、セラミックコンデンサの故障の主な原因は機械的な損傷です。電気的な故障の症状としては、静電容量の低下や回路の短絡・開放として現れます。また、温度などの外的な影響を受けて、これらの症状が現れたり消えたりする場合もあります。セラミックコンデンサのクラックは、目で見てわかる場合もあれば、小さすぎて見えない場合や、実装されたデバイスの下面や端子の縁に隠れている場合もあります。機械的な損傷は、一般にいくつかのメカニズムのうちの1つによってもたらされます。

- 基板組立時やコネクタの嵌合力、手荒な扱い等による基板のたわみ

- 動作温度サイクルや組み立て作業による熱応力

- 組み立て前や組み立て時の誤った取り扱いによる直接的な損傷

セラミック材料、端子、およびプリント基板との機械的結合が強いため、積層セラミックチップ(MLCC)タイプが最も頻繁にクラックの犠牲になっています。スルーホールやリードフレーム実装のデバイスは、端子が比較的長く柔軟であるため、温度サイクルや基板のたわみによるセラミックコンデンサ本体にかかる力が小さくなり、クラックの心配が少なくなります。過酷な使用環境に対応するため、MLCCには、端子とセラミックデバイス本体の機械的柔軟性を向上させたものや、短絡故障のリスクを低減させたものもあります。コンデンサのクラックの原因の多くは組み立てに関連しており、設計者が直接管理することはできません。例えば、ピックアンドプレイス作業で部品を押しつぶしたり壊したりしないようにすることや、使用する組立工程に適切な予熱・冷却時間を設けることは、組立業者の責任です。その他、ソルダーペーストの使用量やペーストの厚みなどは共通の責任ですが、パッドサイズ、基板レイアウト、パッケージの選択などはまさしく設計者の責任です。

MLCCのクラック現象とその回避に関する詳細な議論は、John MaxwellによるCracks:The Hidden Defectなどの工業文献に記載されており、簡潔にするため、ここでは繰り返さないことにします。しかし、これらの苦労して得られた知見から導き出された設計者としての経験則は、次のようなものです。

- 経験豊富で品質にこだわる組立業者を選んでください。

- 熱衝撃を避けてください。噴流はんだ付けや従来のはんだゴテはMLCCの組み立てやリワークにおいて特に危険な方法です。

- 部品サイズを小さくしてください。デバイスが大きくなると、基板のたわみによるストレスが大きくなり、熱衝撃による損傷を受けやすくなります。0805(2012メートル法)またはそれ以下のパッケージのデバイスを推奨します。

- 部品を実装後に基板を分割する際は、基板にたわみが発生しないように細心の注意を払ってください。分割線に沿って手作業でアレイを分割する方法は、最も好ましくない方法であり、ハサミでの切断は少しましですが、やはり同様です。可能であれば、基板に曲げ応力を与えないように、のこぎりなどを使って分離してください。

- MLCCを基板端、コネクタ、取り付け穴、大型・高重量部品、パネル化タブなど、機械的ストレスが基板に加わる可能性のある箇所から遠ざけてください。最小距離0.2インチまたは5mmを推奨します。

経時変化(エージング)

セラミックコンデンサには、誘電体の結晶構造の変化による経時変化で、誘電体材料の初期焼成後の静電容量や誘電正接の変化として現れる現象があります。確立されたパターンに従って測定すると、EIAクラスI誘電体は最も影響が少なく、経時変化がないと広く考えられていますが、EIAクラスII誘電体材料は中程度の影響を受け、EIAクラスIII材料はかなり深刻な影響を受ける傾向にあります。このエージングプロセスは、誘電体のキュリー温度以上の温度で、結晶構造の再形成に十分な時間をかけることでリセット(デバイスのエージングを解除)することができます。温度が高ければ高いほど、必要な時間は短くなります。多くのセラミック誘電体のキュリー温度は、多くのはんだ付けプロセスで生じる温度よりも低いため、デバイスは組み立て中に少なくとも部分的にエージングが解除される可能性があります。

このデバイスのエージング挙動は、通常「最終加熱時」の静電容量に対する「10倍時間ごとの静電容量変化率」として理解されます。最終過熱時は最後にデバイスをキュリー温度以上に加熱し、結晶構造を完全に変化させたときです。つまり、経時変化率(-)5%のコンデンサは、100uFの場合、オーブンから出して1時間、10時間、100時間後にそれぞれ約95、90、85uFになると予想されます。このため、デバイスの公称静電容量がどの程度であるべきか、また、デバイスが未使用で梱包されたまま棚に置かれていても、その静電容量が継続的に変化するのかという疑問が生じます。業界標準のEIA-521とIEC-384-9はこの問題に言及しており、基本的にデバイスは最後に加熱してから1000時間(約42日)後に規定の許容値を満たす必要があると述べています。次の10倍時間(10K時間、100K時間)は、それぞれ1年強、11年強という計算になります。厄介なことに、誘電体のキュリー温度までは、一般にデバイスの温度上昇によってエージングが加速されるため、エージングの進行は温度に依存します。

経年劣化により、デバイスが規定の許容範囲外に見える可能性があるため、製品の設計および製造テスト担当者はその事実に注意することが重要です。最近リフローされた組み立て品のテストでは、静電容量値が少し高くなると予想され、デバイスが古くなっても適切に機能するように十分なマージンを設計する必要があります。電力変換回路では、セラミックコンデンサが補償回路やフィルタ素子として回路の制御ループに強い影響を与えることが多いため、この効果が深刻な危険をもたらす可能性がある場合の良い例です。組み立て時にコンデンサがエージングを解除されることで安定しているように見えるシステムでも、経年劣化による静電容量の損失が制御ループのダイナミクスに影響を与え、時間の経過とともに安定性が低下していくことがあります。特に、経時変化による静電容量値の安定性を重視するのであれば、経時変化の激しいコンデンサは避けるべきでしょう。もしSisyphus(ギリシャ神話)が21世紀の人物だったら、面実装型Y5Vセラミックチップコンデンサを使って作られたアクティブフィルタを調整することが彼の任務だったかもしれません......。

ピエゾ効果/マイクロフォニックス

IECクラス2(EIAクラスII、III)のセラミック誘電体は、圧電体としての性質が顕著であり、電気的領域と機械的領域の間の変換メカニズムが少なからず存在することになります。圧電体に電圧をかけると機械的に変形し、逆に機械的に変形させると圧電体に電圧が現れます。特に面実装型MLCCでは、コンデンサとプリント基板との機械的結合が強いため、この問題が発生することがあります。コンデンサにかかるリップル電圧は耳障りな音に変換され、一方、外部からの機械的な振動は信号として電子回路に結合されることがあります。クラス1の誘電体を用いたセラミックコンデンサは、圧電効果をほとんど示さないため、影響を最も受けにくくなります。しかし、静電効果による電気-機械変換メカニズム(すべてのコンデンサに内在)は依然として存在するため、クラスIデバイスでは一般的に無視できるレベルではありますが、マイクロフォニック効果は依然として存在します。

電極の冶金術

MLCCの電極材料は、ノーブルメタル電極(NME)系と(BME)系と呼ばれる2つの一般的な冶金術のいずれかに従っています。ほとんどのアプリケーションでの一般的な選択基準にはなりませんが、この2つの技術には注意すべき特性の違いがあります。ノーブルメタル電極は、パラジウムと銀の合金が一般的で、ノーブルメタル(特に酸素と比較的反応しない金属)は高価であることから、貴金属電極(PME)と呼ばれることもあります。これらの電極材料は、反応性が低いから使われているのであって、高価だから使われているわけではないので、前者の呼び方が正しいとも言えますが、理屈とマーケティングは一致していないようです......。卑金属電極はニッケル系が一般的です。

セラミック誘電体の焼成に必要な高温で、電極金属がどのように化学反応するかは、生産上の大きな問題です。ノーブルメタル電極系は、高温でより多くの酸素の存在に耐えることができるため、大気圧炉や、硬化に酸素を必要とする誘電体フォーミュレーションを用いて製造することができます。卑金属電極系は高温での酸素に対する耐性がないため、別の装置や誘電体フォーミュレーションで製造する必要があります。NME方式は当初から採用されていた方式であり、信頼性や業界経験の蓄積という点ではメリットがあります。そのため、本稿執筆時点では、高信頼性かつMILスペックの製品の多くがこのプロセスで製造されています。主な欠点は、電極材料のコストが高いことと、材料やプロセスの違いにより、NMEデバイスでは一般的に厚い誘電体層が使用されるため、BMEデバイスに比べて体積あたりの達成可能な静電容量が低くなることです。

デバイスの機能、オプション、およびターゲットとするアプリケーション

車載用

車載用として販売されているコンデンサは、自動車などの機械的な負荷がかかる環境で使用されることを想定して設計されています。また、一般的には、Automotive Electronics Council(車載電子部品評議会)によって確立されたAEC-Q200規格のような、ESD、端子にかかる機械的な力、サージ電圧など、さまざまなストレスメカニズムに対する試験方法と性能レベルを規定したプロトコルに従って生産・試験されています。

ESR制御

「ESR制御」タイプとして指定されたコンデンサは、容量と寄生インダクタンスによって生成されるL-C回路の「Q」値を低減するために、ESRを意図的に少し高くして設計されています。これは、電源レールのデカップリングのアプリケーションなど、適度なESRが存在することでトレースインダクタンスを持つコンデンサの「リンギング」を減衰させたり、並列コンデンサ間の反共振状態を避けるのに役立ちます。

エポキシ樹脂実装

エポキシ樹脂実装デバイスは、通常のはんだ付けではなく、導電性接着剤による実装を想定しています。違いは主に端子の仕上げメッキに使用される材料にあり、使用する実装方法に適した良好な接合を実現するために異なります。エポキシ樹脂実装デバイスは、通常のはんだ付けではうまくいきませんし、その逆も同様です。エポキシ樹脂実装は、温度変化の激しい車載用途などにおいて、はんだ接合に比べ機械的柔軟性が高く、回路基板、はんだ接合部、およびコンデンサ本体の熱膨張係数の違いから発生する機械的ストレスを低減させることができます。また、液晶パネルのような熱に弱いアプリケーションにはエポキシ樹脂実装が有効です。

フローティング電極

「フローティング電極」タイプと呼ばれるデバイスは、複数のコンデンサを実質的に直列に接続し、内部電極をデバイスのどちらの端子にも接続せず、「フローティング」状態にしたものです。この工法の目的は、主にコンデンサのクラックの二次的影響として発生する短絡故障モードのリスクを低減することですが、ESDやサージ電圧に対する堅牢性という点でもメリットがあります。

高温

「高温」タイプに指定されたデバイスは、当然のことながら、一般的な電子機器が遭遇する温度以上の用途を想定しています。一般に、この呼称は「広い温度範囲」を意味するため、電子機器の一般的な動作温度範囲の下限まで使用できるように指定される傾向があります。しかしながら、この呼称を持つほとんどのデバイスが、「セラミックコンデンサ」の中でも温度やDCバイアスに対してかなり優れたパラメータ安定性を示すことはあまり知られていません。

高電圧/Arc Guard™/ArcShield™

「高電圧」または独自の耐アーク表示があるコンデンサは、電子機器に通常使用される電圧を超えるアプリケーションで使用するために設計されています。何をもって「高電圧」とするかはメーカーによって異なりますが、その境界線は100Vから1kVの範囲にあると思われます。このような電位では、端子間、あるいは端子ともう一方の端子に接続された電極間が、デバイスの外装を貫通して表面アークを発生させ、MLCC技術の複雑化を招き始めます。もちろん、これは良いことではありません。表面アーク放電は、どのような部品でも十分な高電圧がかかると問題になりますが、MLCC技術は特に脆弱であると言えます。MLCCはコンパクトな構造であるため、2つの端子とその接続電極が非常に近接し、絶縁破壊やアーク放電の危険性が高くなるからです。そのためにサイズを大きくすることも可能ですが、その場合、デバイスにクラックが入るリスクが大きくなります。Arc Guard™やArc Shield™シリーズなどのデバイスは、これらの影響を軽減し、絶縁破壊による故障リスクと機械的クラックのトレードオフ方程式を改善するように設計されています。

高Q/低損失/低誘電正接

高Qタイプ、低損失タイプ、あるいは低誘電正接タイプとして販売されているデバイスは、ESRを最小化するように設計されています。一般的にこれらのデバイスはクラスIの誘電体材料で作られており、周波数識別のために理想に近いコンデンサが望まれるRFやその他の高周波アプリケーションで使用されます。

ブリーダ抵抗器内蔵

この呼称のデバイスは、無通電時にコンデンサに電荷が残ったり、発生しないように、並列接続された抵抗を内蔵したデバイスです。本稿執筆時点で、Digi-Keyはこの名称の付いた品番を3つだけリストアップしていますが、いずれも非在庫品で、高額な値札が付けられています。なぜでしょう?データシートの最初のページに記載されている推奨アプリケーションには、「起爆装置」や「電子式信管」などがありますが、これはほとんどのコンデンサのデータシートには記載されていないものです。(アプリケーションノートはありません…)

低ESL

低ESLセラミックコンデンサは、直列インダクタンスを最小限に抑えるように設計されています。面実装型MLCC の場合、このインダクタンスのほとんどは部品自体に固有のものではなく、むしろパッケージの形状や回路に接続するリード線に関係するものです。したがって、低 ESL MLCC は、ほとんどの場合、標準的なデバイスの幾何学的およびリード構成のバリエーションです。

多端子低ESLデバイスは、コンデンサの理論的な端子1つに対して複数の物理端子を用い、それらを交互に挟み込むことで電流の出入りで生じる磁界を大きくキャンセルし、低インダクタンスを実現するものです。

逆ジオメトリ(長辺電極)セラミックコンデンサは、他のデバイスのようにコンデンサの両端ではなく、長辺にデバイスの端子を配置するのが一般的です。

スタック型低ESLセラミックコンデンサは、複数のMLCCデバイスをリードフレームで結合することで、単一のユニットとして取り扱い、組み立てることができ、クラックやマイクロフォニック効果のリスクを低減する利点があります。このようなデバイスを「低ESL」と表現するのは、マーケティング上の策略のようなものです。何故なら、例えばコンデンサ技術が異なるリンゴとオレンジのコンデンサを比較しているからです。同じセラミックコンデンサをプリント基板に直接取り付ける場合と比較して、リードフレームに取り付けると(基板より高く持ち上げられ)、ESLは著しく大きくなります。

低ESL MLCCのX2Y記述子は商標であり、「X1Y2」のような類似の安全指定子と混同しないように注意してください。2つのデバイスグループには、使用される理由に関して多少の類似点がありますが、デバイス自体は根本的に異なります。低ESL X2Yコンデンサは、わずか6.3Vの定格で、毎回短絡故障が許されます。一方、安全規格のデバイスは、kVレベルのサージに耐え、短絡故障モードを徹底的に避けなければなりません。

しかし、X2Y低ESLコンデンサは、低電圧電源のデカップリングやコモンモードフィルタリングなどのアプリケーションに大きなメリットがあります。それらの際立った特徴は、4端子構造です。2つの端子は電気的に接続され、「パススルー」接続として、またデバイス内の2つの別々のコンデンサの共通端子として機能し、それぞれのコンデンサは残りの1つの端子を第2の電極接続に使用します。この配置の形状により、デカップリング用途やコモンモード抑制などのレイアウトに関わるインダクタンスを低減することができます。

薄型

薄型コンデンサは、高さ方向の制約が強いアプリケーションで使用するために、同程度の長さと幅の一般的なデバイスよりも薄く作られています。厚さ0.006インチ(0.15mm)までのデバイスを利用できます。ただし、これらのデバイスの厚みが薄くなると、ボードのたわみによるクラックが発生しやすくなり、これらのデバイスによって高さを1~2ミリメートル減らす必要があるアプリケーションでは、より薄い(したがってより柔軟な)回路基板も使用される可能性がありますので、設計、組み立て、取り扱いに注意が必要です。

軍用

米軍の標準品番体系で調達された「軍用」指定品は、複数の供給元で製品の一貫性を確保するため、軍が定めた仕様で生産されています。

従来の「MIL規格」は、何を作るかだけでなく、どのように作るかを規定し、異なるサプライヤからの製品の均一性、互換性を保証するためのものでした。新しい「MIL-PRF規格」はパフォーマンス・ベースで、製品がどのように機能しなければならないかを規定していますが、目的を達成するための正確な方法はメーカーに大きく委ねられています。後者のアプローチでは、メーカー間や時間経過による製品動作のばらつきのリスクが多少高まるものの、柔軟な対応が可能になり、新しい技術や製造工程を採用する余地が大きくなります。

いずれにせよ、MIL規格で調達された「真の」軍用製品は、膨大なテストと文書化の必要性から、かなり高価になりがちです。その中間的な存在として、MIL規格で生産されながら標準的な市販品として販売されている製品もありますが、その場合は膨大な資料はありません。

非磁性

非磁性コンデンサは、磁石に引き寄せられたり、悪影響を受けたりしない材料で作られており、置かれた磁界に影響を与えません。最終製品がこれらの特性を保持していることを保証するために、多くの場合製造後にスクリーニングを行ないます。このような製品は、磁場の影響を受けたり、応用回路や他の機器の動作に影響を与えるような磁場を保持することが好ましくない、医療用画像診断装置、ナビゲーションシステム、実験装置などのアプリケーションに使用されます。

オープンモード

「オープンモード」デバイスとして販売されているMLCCは、機械的クラックの結果として発生しうる短絡や低インピーダンスの故障モードのリスクを低減するように設計されています。この目的を達成するために、2組の電極の重なり面積を小さくし、基板のストレスクラックの典型的な経路が電極の重なり部分を通らないようにするのが一般的な方法です。そのため、コンデンサ内の有効面積が減少し、その結果、所定のパッケージサイズで達成可能な最大容量値が減少します。

この方法は、フローティング電極技術やソフトターミネーション技術と組み合わせることで、クラックによるMLCC故障のリスクをさらに低減することができます。MLCCをオープンモードにすることで、短絡故障のリスクは大幅に軽減されますが、それでも故障の確率はゼロではないことに留意する必要があります。短絡故障の確率をさらに下げる必要がある場合、2つの直列接続されたデバイスを互いに90度傾けて使用することが業界の文献に提案されています。

ソフトターミネーション/フレキシブルターミネーション

ソフトターミネーションやフレキシブルターミネーションとして販売されているMLCCは、金属端子とセラミックコンデンサ本体の間の結合が、標準的なMLCCよりも機械的な適応力が高くなるよう設計されています。これにより、基板のたわみや温度サイクルによってセラミック材料にかかる応力を軽減し、クラックの発生リスクを低減しています。