特點

MachXO2 分接板(DigiKey 零件編號 220-2625-ND 是一款低成本可編程邏輯元件(PLD)開發板。MachXO2 是一款低功耗 FPGA,配備基於 ASIC 閘的強化嵌入式功能塊(EFB)。本教學將涵蓋以下設計主題:

- 周邊裝置擴充應用介紹及概述

- MachXO2 內部振盪器實例化

- 透過 FPGA 架構中的 Wishbone 匯流排使用嵌入式功能塊

- 自訂 VHDL 元件設計與實例化,包括按鈕解彈跳器、正交編碼器介面(QEI)、格瑞解碼器(Gray Decoder)、Wishbone 匯流排控制狀態機和資料流狀態機

- 用於驗證的硬體測試模組,例如七段顯示 (SSEG) 編碼器和顯示多工器

介紹

本參考設計使用 MachXO2 低成本 FPGA 作為基於 SPI 的周邊裝置擴充設備。在工業控制和消費性電子等許多應用中,正交編碼器、格瑞解碼器和觸覺開關陣列可用作人機介面(HMI)。此類設計的主要要求是大量使用微控制器/處理器引腳。正交編碼器通常與特殊的介面外設配合使用,以追蹤輸入旋鈕的位置,且幾乎不佔用處理器資源。許多微控制器/處理器的編碼器介面有限。本參考設計使用 machXO2 FPGA 透過 SPI 通訊將兩個旋轉編碼器(一個正交編碼器和一個格瑞解碼器)以及一組按鈕作為 HMI 連接到 ARM Cortex M3 裝置。通常需要 14 個引腳才能處理的事情現在只需 4 個引腳即可完成。輸入已進行解彈跳處理以避免硬體彈跳;按鈕也可以使用 RC 濾波器進行解彈跳處理,以節省使用者邏輯。格瑞編碼器可選解碼為標準十六進位。此設計具有極強的可擴展性,可透過實例化更多解彈跳電路、正交編碼器介面、格瑞解碼器和觸覺按鈕陣列來包含更多輸入設備。

背景

MachXO2 分接板是一款低成本、低功耗的解決方案,適用於多種輸入和控制應用。與使用 FPGA 架構相比,在提供的硬 ASIC 閘中實作所有 EFB 功能時,EFB 可以節省超過 500 個 LUT。嵌入式功能區塊包含以下硬 ASIC 周邊裝置,跟據 Lattice 技術手冊 TN1205:

- 兩個 I2C 內核

- 一個 SPI 內核

- 一個 16-bit 定時器/計數器

- 使用者快閃記憶體(MachXO2-640 及更高密度)

- 動態 PLL 配置設定接口

- 透過 I2C 和 SPI 介面連接片上電源控制器

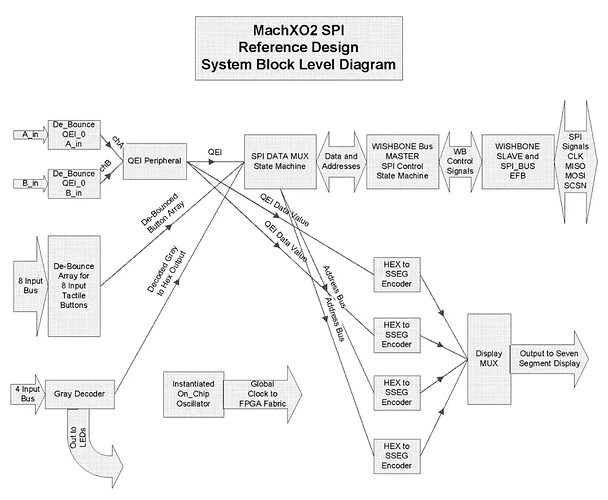

嵌入式功能塊的周邊裝置控制是透過使用 Wishbone 匯流排介面(一種符合 OpenCores 標準的標準匯流排)來實現。此介面可以透過兩個主控制器之一的存取,一個是 LatticeMico8,另一個是 FPGA 結構內的自訂狀態機。本參考設計使用狀態機控制 Wishbone 匯流排並存取 SPI。另一個狀態機負責資料操作和控制,控制通往 Wishbone 匯流排狀態機的資料路徑。系統框圖如下圖 1 所示。

圖 1 MachXO2 SPI 系統方塊圖

應用

建構電路

實例化晶片上振盪器和嵌入式功能塊(EFB)

為此,需要在頂層 HDL 封裝檔中呼叫 MachXO2 函式庫和套件。請參考隨附的 top.vhd 檔案來觀察該應用。它在 top.vhd 檔案的頂部顯示如下:

MACHXO2 庫;

使用 MACHXO2.components.all;

元件必須包含在頂層架構定義和主要描述之間,這也稱為聲明部分。標稱頻率可以在元件聲明和通用對應中的實例化中定義。此特定設計運作頻率為 38MHz。

要在 EFB 中實例化 SPI 周邊裝置,需要使用 IP Express;這可以透過點擊 Diamond 工具列中的 IP Express 按鈕來執行。從左側的內核清單中選擇 EFB,即可開啟 EFB 配置窗口,如下圖 2 所示。

圖 2 EFB 配置視窗

SPI 設定配置完成後,點擊「產生」按鈕將建立 SPI 匯流排的 HDL 文件,並透過 Wishbone 匯流排進行介面。有關此過程的詳細信息,請參閱 Lattice技術筆記 TN1246《MachXO2 設備中使用用戶閃存和強化控制功能參考指南》。

自訂 VHDL 元件設計和實例化

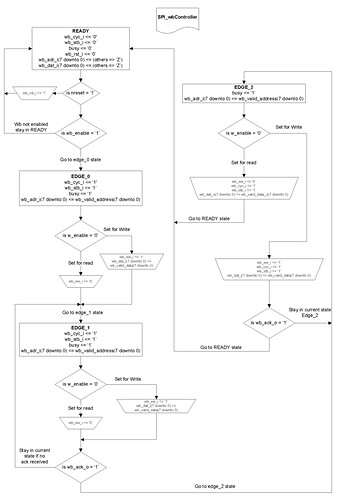

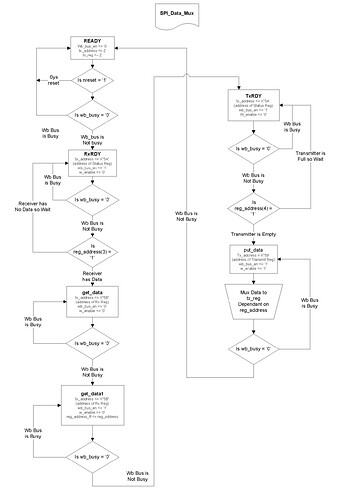

設計包含按鈕解彈跳器、正交編碼器介面(QEI)、格瑞解碼器、Wishbone 匯流排控制狀態機和資料流狀態機。按鈕解彈跳器用作基於時間的濾波器,根據輸入的持續時間更新輸出。對於需要計算輸入發生次數的電路,按鈕解彈跳器更為關鍵。QEI 模組受益於解彈跳電路,因為它不會計數編碼器內部機械振動產生的錯誤輸入。QEI 透過使用雙通道異相輸入來追蹤旋鈕的位置。兩個通道的相位差用於遞增或遞減計數器。該模組還能夠追蹤旋鈕在恆定時間段內的旋轉距離,以用於速度應用;此功能已在本設計的模組中被註解掉。格瑞解碼器是一種快速方法,可以根據格雷碼旋鈕的位置將格雷碼序列轉換為標準順序十六進位序列。Wishbone 匯流排控制和資料流狀態機是設計中較為複雜的兩個元件。為了全面理解上述狀態機如何與 Wishbone 匯流排協同運作,請參考 Lattice TN1246 以了解 Wishbone 的讀寫訊號及相關時序。

Wishbone 匯流排控制和資料流狀態機的狀態流程圖分別如下圖 3 和 4 所示。

圖 3 Wishbone 控制狀態機狀態圖

圖 4 SPI 資料流狀態機

硬體測試模組

本設計中使用了多個元件來驗證每個輸入暫存器中保存的值。具體方法是將數值顯示在外部七段顯示器和分接板上的 LED 陣列上。SSEG 顯示器上的最高有效半位元組顯示 SPI 主控傳送給 MachXO2 的位址。最低有效半位元組顯示從 MachXO2 內部暫存器取得的正交編碼器的位置。板載 LED 顯示灰階轉十六進位解碼器的輸出。為了操作 SSEG 顯示器,使用了多個支援組件,例如十六進位轉 SSEG 顯示編碼器和顯示多工器。這些組件用於控制進入顯示器的數據和陽極的切換。顯示器透過一個 17-bit 定時器以大約 190Hz 的頻率刷新。七段顯示器如下圖 5 所示。

圖 5 用於 SPI 驗證的七段顯示器

請注意 OLED 螢幕上顯示的 Arm Cortex M3(SPI 主控)數據(如下圖 6 所示)與來自 MachXO2(SPI 從屬)的 SSEG 顯示器上的數據(如上圖 5 所示)如何匹配。來自 Wishbone 控制狀態機的忙訊號也已透過引腳 142 路由到外部以供觀察。

圖 6:Arm Cortex M3 OLED 資料與 FPGA SSEG 顯示資料匹配

VHDL 元件層次結構如下圖 7 所示。這個結構是在 Diamond 中透過點擊 Diamond 工具列中的「生成層次結構」按鈕產生的。

圖 7 MachXO2 SPI 周邊裝置擴充層級結構

功能、限制和變更

本參考設計使用 Lattice Diamond 1.4.2.105 版本開發,並結合 Synopsis(Synplify Pro)和 Aldec(Active HDL 8.3 Lattice WEB Edition II)的支援軟體。Lattice Diamond 可作為獨立的開發環境,與第三方綜合和模擬軟體搭配使用。

總結

本參考設計展示如何使用 MachXO2 作為周邊裝置擴充。透過八個正交編碼器、兩個格瑞解碼器和八個按鈕陣列,處理器有效 IO 引腳數可從 32 個減少到僅 4 個,用於 SPI 通訊。

更多資訊

更多設計支援、產品教學、應用筆記、使用者指南及其他文檔,請訪問 Lattice 網站。

附錄:下載

完整的 MachXO2 SPI 周邊裝置擴充(適用於 HMI 應用)VHDL 檔案可在此下載。

SPI_Peripheral_Expansion.zip (779.2 KB)