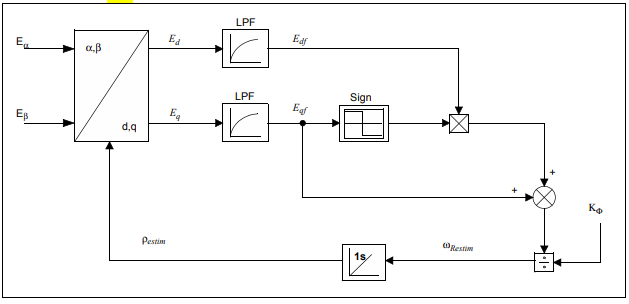

位相同期回路(PLL) のブロック図には、通常、位相検出器(PD)、ループフィルタ(LF)、および電圧制御発振器(VCO) の3つのコアモジュールが含まれます。場合によっては、周波数分割器や信号前処理ユニットが追加されることもあります。そのコアロジックは、閉ループのフィードバックにより、入力信号の周波数/位相と出力信号の周波数/位相を正確に同期させることです。

I. PLL(位相同期回路)の原理

(出典:Microchip)

PLL(位相同期回路)のコアロジックは、閉ループフィードバックによって入力信号の周波数/位相と出力信号の周波数/位相を正確に同期させることです。

- 位相検出器(PD): 入力された速度関連信号(モータ電流の交流信号、エンコーダパルス信号など)とVCOの出力信号との位相差を比較し、この位相差を誤差電圧に変換します。

- ループフィルタ(LF): 高周波ノイズや過渡的な干渉を抑制するために誤差電圧をフィルタリング(ローパスフィルタリングなど)し、滑らかな制御電圧を出力します。

- 電圧制御発振器(VCO): 制御電圧に応じて出力信号の周波数/位相を調整し、入力信号の特性に徐々に近づけます。最終的に「位相ロック」を実現し、入力信号と出力信号の周波数が一致し、位相差が安定します。

II. なぜPLLと高次フィルタリングはマルチレベル速度サンプリングにおいて干渉防止と精度を保証できるのでしょうか?

マルチレベル速度サンプリング(Multi-Level Speed Sampling)では、速度による信号特性の違い(低速では微弱信号、高速では高周波信号など)、環境からの電磁干渉、センサノイズなどの問題に対処する必要があります。PLLと高次フィルタリングは、これらの課題をさまざまな側面から解決します。

1. PLL(位相同期回路)ソリューション: 同期トラッキングによる周波数不一致と動的誤差の排除

マルチレベル速度サンプリングでは、回転速度の変化により、関連する信号(電流、パルスなど)の周波数が大きく変動します。PLLの中核的な価値は、サンプリングが信号のリアルタイム特性に一致するように、信号周波数を動的にロックすることにあります。

- 周波数エイリアシングの抑制: ナイキスト標本化定理によれば、サンプリング周波数は信号の最大周波数の2倍以上である必要があります。PLLはVCOを介してサンプリングクロック周波数を動的に調整し、常に入力信号の周波数に追従します。これにより、固定サンプリングレートに起因する低周波数域での冗長なオーバーサンプリングや、高周波数域でのアンダーサンプリングによるエイリアシングを回避できます。

- 動的干渉への耐性: 速度が急激に変化した場合(例えばマルチレベル切替時)、入力信号の周波数は急激に変動します。PLLのループフィルタは誤差信号を平滑化し、VCOは迅速に応答して出力周波数を調整することで、遷移プロセス中でも安定した信号追従性を確保します。

- 位相ノイズの影響の削減: 環境による電磁干渉は、信号の位相ジッタの原因となります。PLLの閉ループフィードバックは、位相補正によってこのジッタを相殺し、出力信号の位相を安定に保つことができます。

まとめ

マルチレベル速度サンプリングの中核となる課題は、信号周波数の動的変動と干渉ノイズの混入です。PLLは、周波数追従と位相ロックによってサンプリングと信号特性のリアルタイム同期を保証し、動的不一致エラーを排除します。

関連製品

関連アプリケーションノート

FOCに関する他の資料

- なぜDSPを使用して三相永久磁石同期モータ(PMSM)を制御するのでしょうか?

- 3つのモータ制御技術の比較:FOC、V/f制御、台形波6ステップ制御(BLDC)

- なぜフィールドオリエンテッド制御(FOC)を使うのでしょうか?

- フィールドオリエンテッド制御(FOC)アルゴリズムにおけるクラーク変換とは何でしょうか?

- フィールドオリエンテッド制御(FOC)アルゴリズムにおけるパーク変換とは何でしょうか?

- なぜPLL(位相同期回路)はマルチレベル速度サンプリングにおいて干渉防止と高精度を確保できるのでしょうか?